7-9

REFRESH CONTROL UNIT

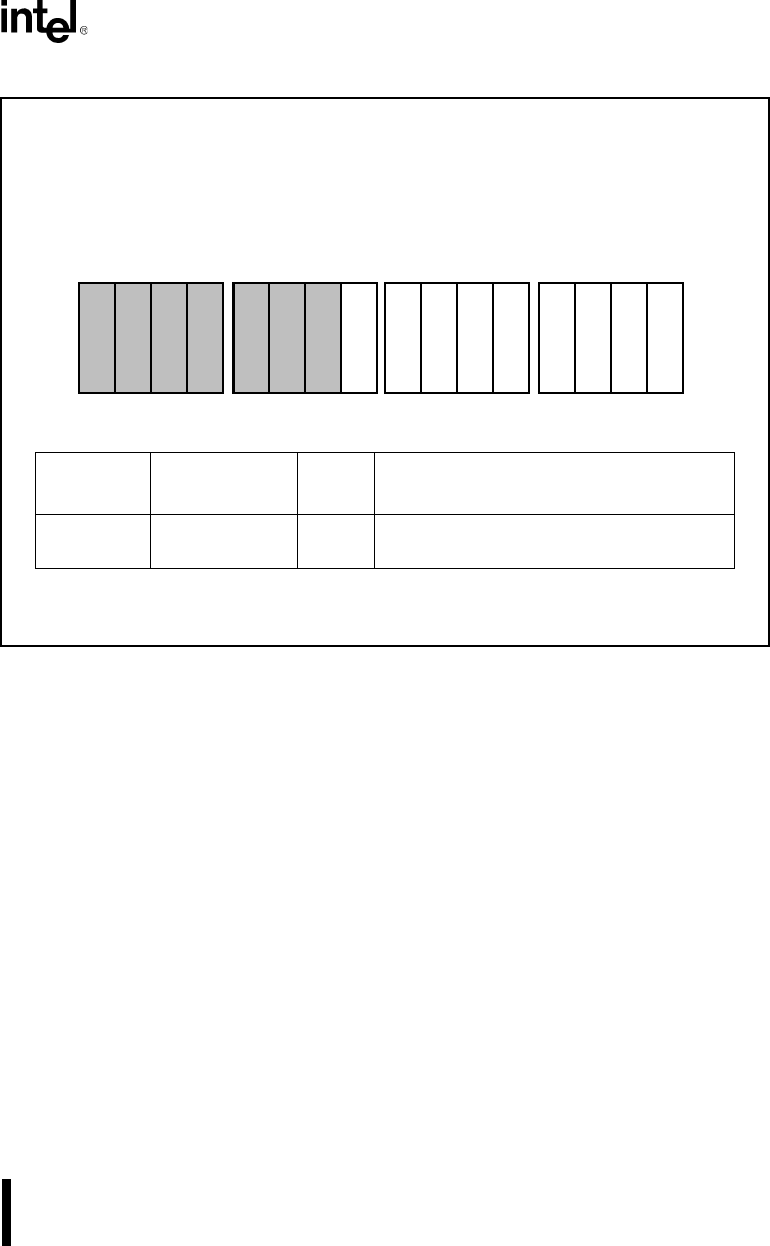

Figure 7-7. Refresh Clock Interval Register

7.7.2.3 Refresh Control Register

Figure 7-8 shows the Refresh Control Register. The user may read or write the REN bit at any

time to turn the Refresh Control Unit on or off. The lower nine bits contain the current nine-bit

down-counter value. The user cannot program these bits. Disabling the Refresh Control Unit

clears both the counter and the corresponding counter bits in the control register.

Register Name: Refresh Clock Interval Register

Register Mnemonic: RFTIME

Register Function: Sets refresh rate.

Bit

Mnemonic

Bit Name

Reset

State

Function

RC8:0 Refresh Counter

Reload Value

000H Sets the desired clock count between refresh

cycles.

NOTE: Reserved register bits are shown with gray shading. Reserved bits must be written to a

logic zero to ensure compatibility with future Intel products.

15 0

R

C

0

R

C

1

R

C

2

R

C

3

R

C

4

R

C

5

R

C

6

R

C

7

R

C

8

A1288-0A