D-5

INSTRUCTION SET OPCODES AND CLOCK CYCLES

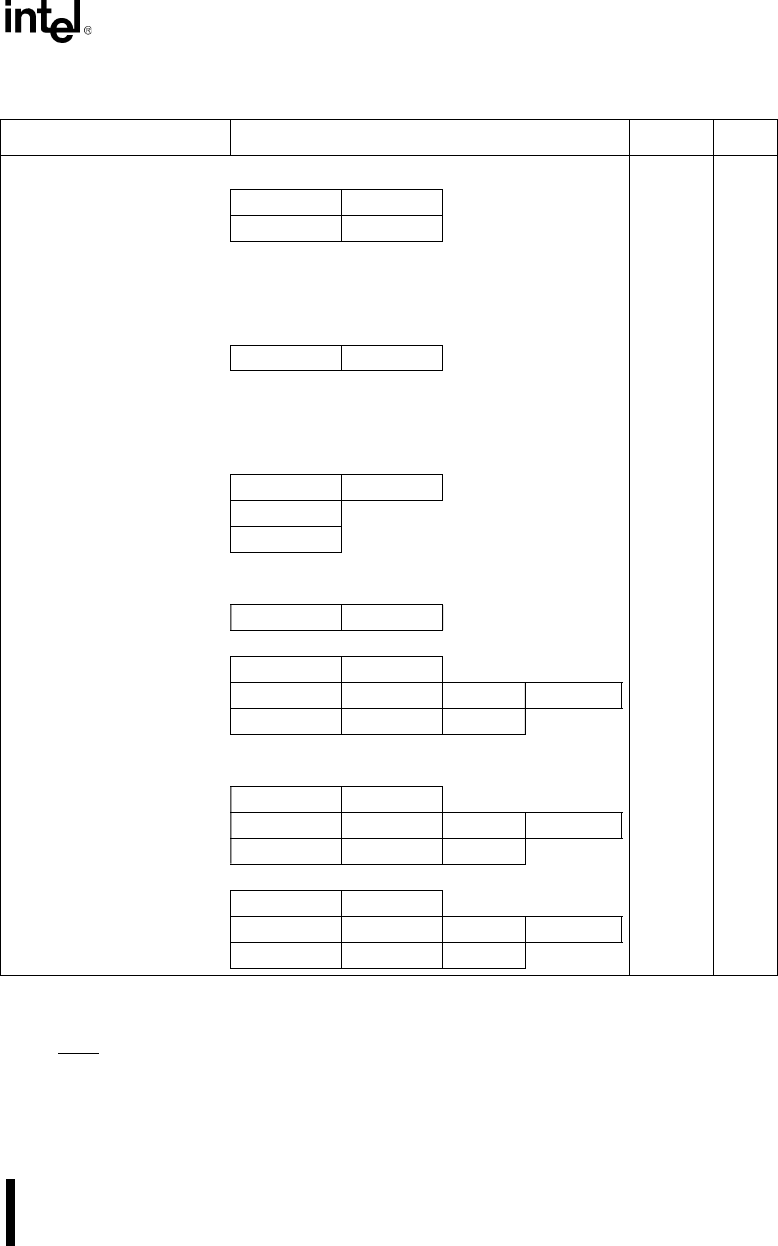

ARITHMETIC INSTRUCTIONS (Continued)

AAM = ASCII adjust for multiply 1 1 0 1 0 1 0 0 0 0 0 0 1 0 1 0 19

DIV = Divide (unsigned) 1 1 1 1 0 1 1 w mod 110 r/m

register-byte

29

register-word

38

memory-byte

35

memory-word

44

IDIV = Integer divide (signed) 1 1 1 1 0 1 1 w mod 111 r/m

register-byte

29

register-word

38

memory-byte

35

memory-word

44

AAD = ASCII adjust for divide 1 1 0 1 0 1 0 1 0 0 0 0 1 0 1 0 15

CBW = Convert byte to word 1 0 0 1 1 0 0 0 2

CWD = Convert word to double-word 1 0 0 1 1 0 0 1 4

BIT MANIPULATION INSTRUCTIONS

NOT= Invert register/memory 1 1 1 1 0 1 1 w mod 010 r/m 3

AND = And

reg/memory and register to either

0 0 1 0 0 0 d w mod reg r/m 3/10

immediate to register/memory

1 0 0 0 0 0 0 w mod 100 r/m data data if w=1 4/16

immediate to accumulator

0 0 1 0 0 1 0 w data data if w=1 3/4 (1)

OR = Or

reg/memory and register to either

0 0 0 0 1 0 d w mod reg r/m 3/10

immediate to register/memory

1 0 0 0 0 0 0 w mod 001 r/m data data if w=1 4/10

immediate to accumulator

0 0 0 0 1 1 0 w data data if w=1 3/4 (1)

XOR = Exclusive or

reg/memory and register to either

0 0 1 1 0 0 d w mod reg r/m 3/10

immediate to register/memory

1 0 0 0 0 0 0 w mod 110 r/m data data if w=1 4/10

immediate to accumulator

0 0 1 1 0 1 0 w data data if w=1 3/4 (1)

Table D-2. Instruction Set Summary (Continued)

Function Format Clocks Notes

NOTES:

1. Clock cycles are given for 8-bit/16-bit operations.

2. Clock cycles are given for jump not taken/jump taken.

3. Clock cycles are given for interrupt taken/interrupt not taken.

4. If TEST

= 0

Shading indicates additions and enhancements to the 8086/8088 instruction set. See Appendix A, “80C186

Instruction Set Additions and Extensions,” for details.