8-17

INTERRUPT CONTROL UNIT

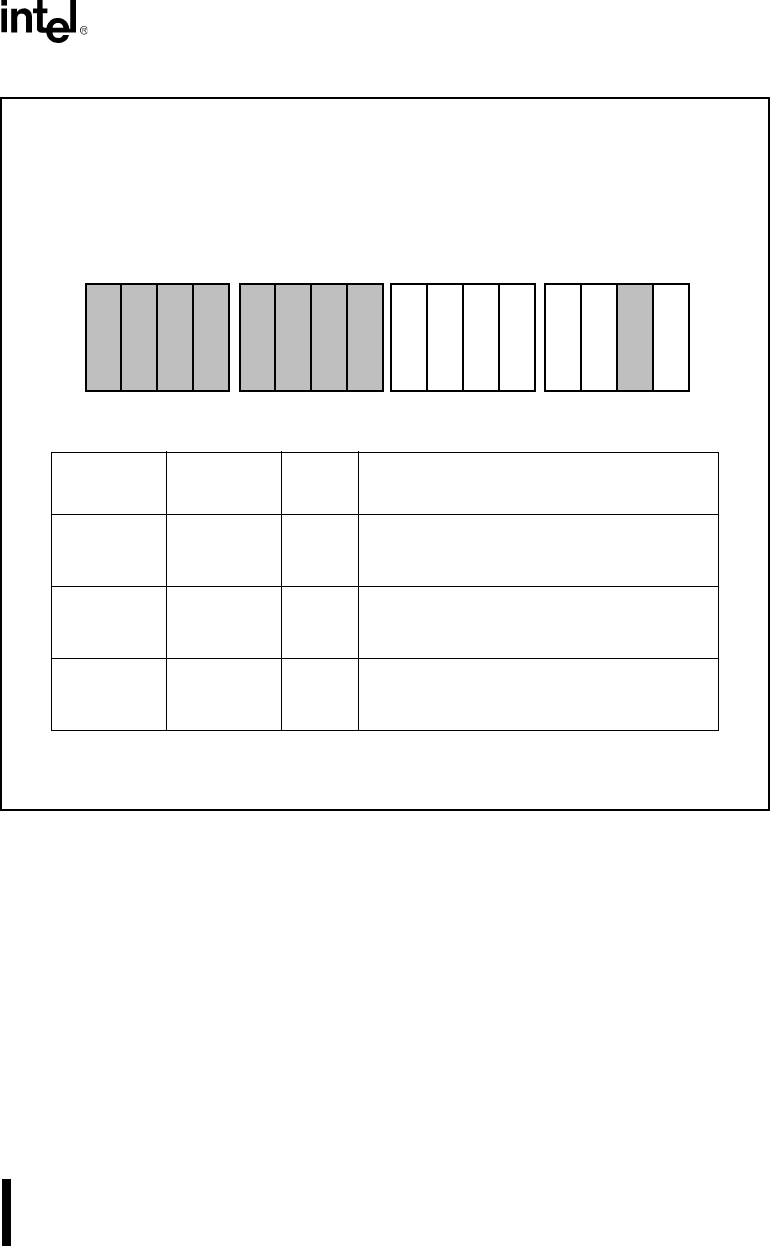

Figure 8-8. Interrupt Mask Register

8.4.4 Priority Mask Register

The Priority Mask register (Figure 8-9) contains a three-level field that holds a priority value.

This register allows you to mask interrupts based on their priority levels. Write a priority value

to the PM2:0 field to specify the lowest priority interrupt to be serviced. This disables (masks)

any interrupt source whose priority is lower than the PM2:0 value. After reset, the Priority Mask

register is set to the lowest priority (seven), which enables all interrupts of any priority.

Register Name: Interrupt Mask Register

Register Mnemonic: IMASK

Register Function: Masks individual interrupt sources

Bit

Mnemonic

Bit Name

Reset

State

Function

INT3:0 External

Interrupt

Mask

0000 0 Set a bit to mask (disable) interrupt requests

from the corresponding external interrupt pin.

DMA1:0 DMA

Interrupt

Mask

0 Set to mask (disable) interrupt requests from

the corresponding DMA channel .

TMR Timer

Interrupt

Mask

0 Set to mask (disable) interrupt requests from

the timers.

NOTE: Reserved register bits are shown with gray shading. Reserved bits must be written

to a logic zero to ensure compatibility with future Intel products.

A1202-A0

15 0

T

M

R

D

M

A

0

D

M

A

1

I

N

T

0

I

N

T

1

I

N

T

2

I

N

T

3