INTERRUPT CONTROL UNIT

8-20

Reading the Poll register (Figure 8-11) acknowledges the pending interrupt, just as if the CPU

had started the interrupt vectoring sequence. The Interrupt Control Unit updates the Interrupt Re-

quest, In-Service, Poll, and Poll Status registers, as it does in the normal interrupt acknowledge

sequence. However, the processor does not run an interrupt acknowledge sequence or fetch the

vector from the vector table. Instead, software must read the interrupt type and execute the proper

routine to service the pending interrupt.

Reading the Poll Status register (Figure 8-12) will merely transmit the status of the polling bits

without modifying any of the other Interrupt Controller registers.

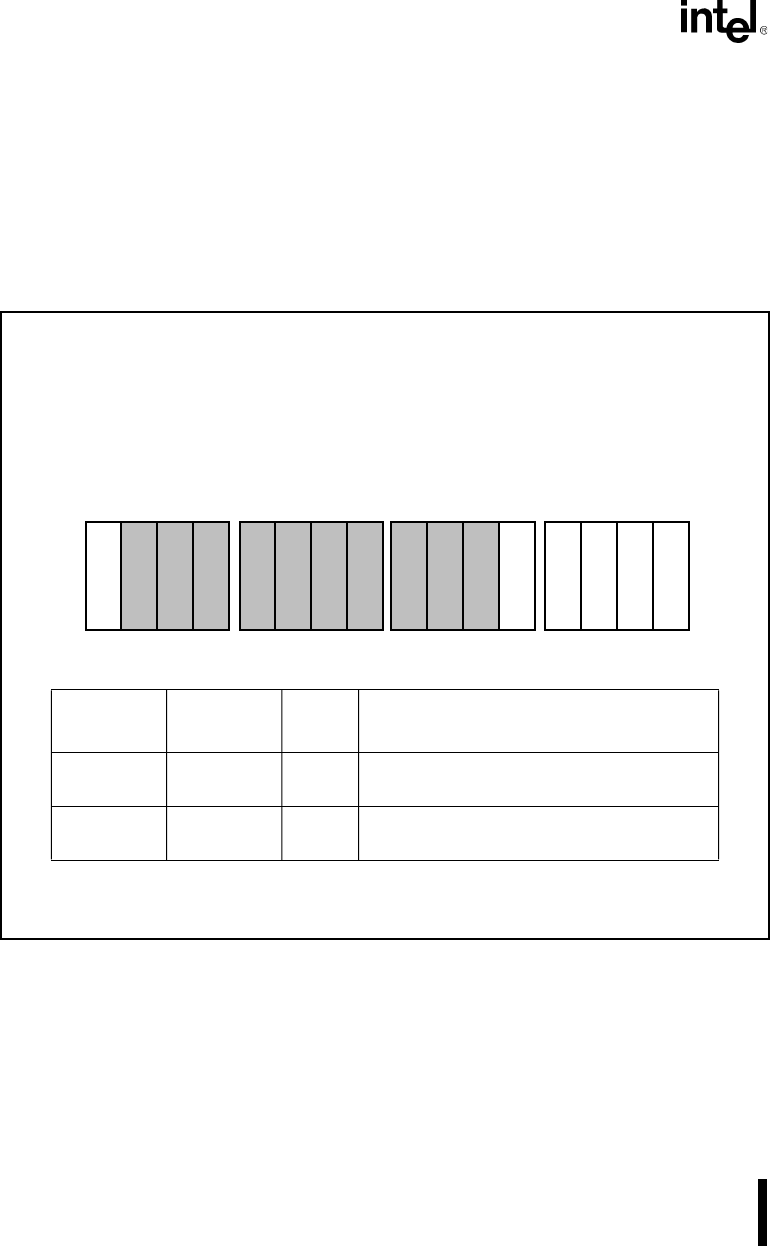

Figure 8-11. Poll Register

Register Name: Poll Register

Register Mnemonic: POLL

Register Function: Read to check for and acknowledge pending

interrupts when polling

Bit

Mnemonic

Bit Name

Reset

State

Function

IREQ Interrupt

Request

0 This bit is set to indicate a pending interrupt.

VT4:0 Vector Type 0 Contains the interrupt type of the highest

priority pending interrupt.

NOTE: Reserved register bits are shown with gray shading. Reserved bits must be written

to a logic zero to ensure compatibility with future Intel products.

A1208-A0

15 0

V

T

0

V

T

2

V

T

3

V

T

4

I

R

E

Q

V

T

1