8-29

INTERRUPT CONTROL UNIT

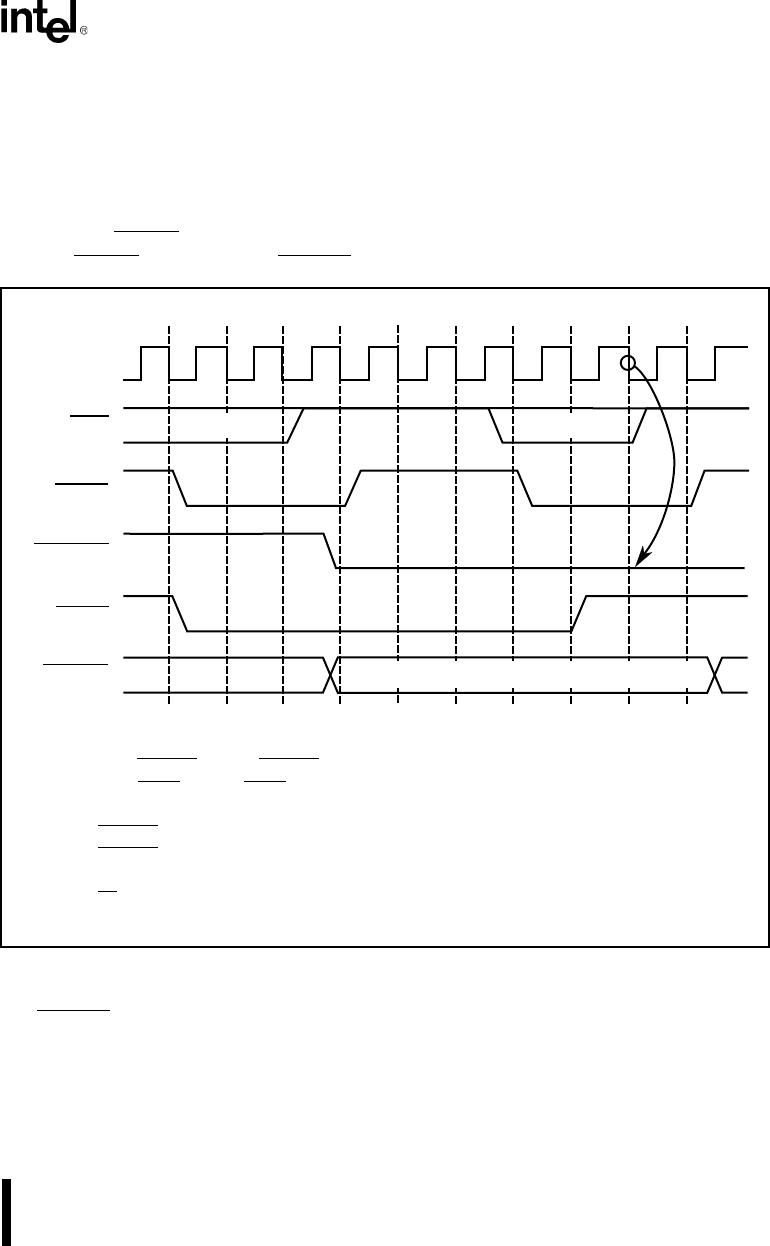

8.5.2 Interrupt Vectoring in Slave Mode

In Slave mode, the external 8259A module acts as the master interrupt controller. Therefore, in-

terrupt acknowledge cycles are required for every interrupt, including those from integrated pe-

ripherals. During the first interrupt acknowledge cycle, the external 8259A determines which

slave interrupt controller has the highest priority interrupt request. It then drives that slave’s ad-

dress onto its CAS2:0

pins (Figure 8-20). External logic must decode the correct slave address

from the CAS2:0

pins to drive the SELECT pin.

Figure 8-20. Interrupt Vectoring in Slave Mode

The SELECT pin is the slave-select input to the Interrupt Control Unit. During the second inter-

rupt acknowledge cycle, the highest-priority slave interrupt controller transfers the interrupt type

of its highest priority interrupt to the CPU. If the Interrupt Control Unit is the highest-priority

slave, it passes the interrupt type to the CPU internally; however, the interrupt acknowledge cycle

still must occur for the benefit of the external 8259A module.

T1 T2 T3 T4

CLKOUT

TI TI T1 T2 T3

LOCK

CAS2:0

S2:0

INTA0

SELECT

NOTES:

1. INT1/SELECT has the SELECT function in slave mode.

2. INT2/INTA0 has the INTA0 function in slave mode.

3. Cascade address is driven by the external 8259A.

4. SELECT must be driven before phase 2 of T2 of the second INTA.

5. SELECT read by processor.

6. ALE is generated for each INTA.

7. RD is inactive.

Slave Cascade Address From 8259A

T4

INTA INTA

A1199-A0