OVERVIEW OF THE 80C186 FAMILY ARCHITECTURE

2-10

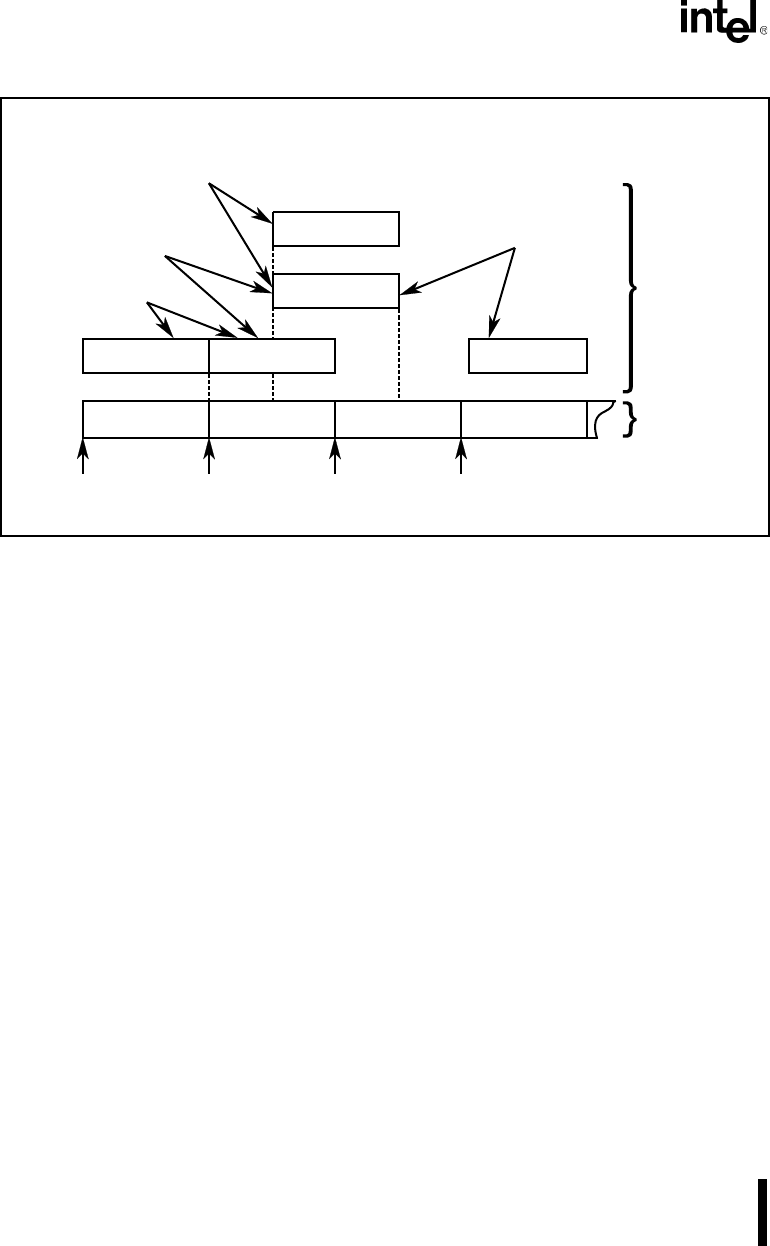

Figure 2-6. Segment Locations in Physical Memory

The four segment registers point to four “currently addressable” segments (see Figure 2-7). The

currently addressable segments provide a work space consisting of 64 Kbytes for code, a 64

Kbytes for stack and 128 Kbytes for data storage. Programs access code and data in another seg-

ment by updating the segment register to point to the new segment.

2.1.8 Logical Addresses

It is useful to think of every memory location as having two kinds of addresses, physical and log-

ical. A physical address is a 20-bit value that identifies a unique byte location in the memory

space. Physical addresses range from 0H to 0FFFFFH. All exchanges between the CPU and

memory use physical addresses.

Programs deal with logical rather than physical addresses. Program code can be developed with-

out prior knowledge of where the code will be located in memory. A logical address consists of

a segment base value and an offset value. For any given memory location, the segment base value

locates the first byte of the segment. The offset value represents the distance, in bytes, of the tar-

get location from the beginning of the segment. Segment base and offset values are unsigned 16-

bit quantities. Many different logical addresses can map to the same physical location. In Figure

2-8, physical memory location 2C3H is contained in two different overlapping segments, one be-

ginning at 2B0H and the other at 2C0H.

Physical

Memory

0H 10000H 20000H 30000H

Fully

Overlapped

Partly

Overlapped

Contiguous

Segment B

Segment C

Segment D

Segment E

Logical

Segments

Disjoint

Segment A

A1036-0A