DIRECT MEMORY ACCESS UNIT

10-10

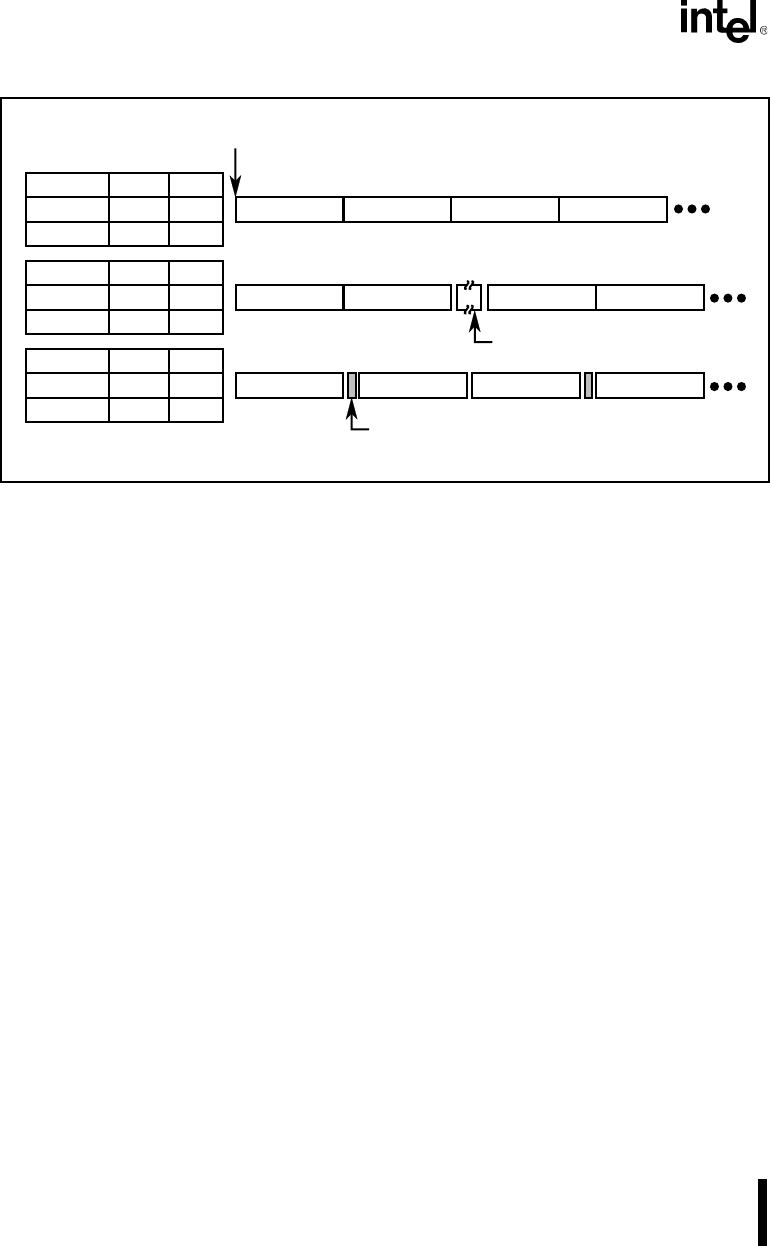

Figure 10-6. Examples of DMA Priority

10.1.10.1.2 Rotating Priority

Channel priority rotates when the channels are programmed as both high or both low priority. The

highest priority is initially assigned to channel 1 of the module. After a channel performs a trans-

fer, it is assigned the lower priority. When requests are active for both channels, the transfers al-

ternate between the two. Channel 1 is reassigned high priority whenever the bus is released (that

is, at the end of a destination-synchronized transfer or when DMA requests are no longer active).

10.2 PROGRAMMING THE DMA UNIT

A total of six Peripheral Control Block registers configure each DMA channel.

10.2.1 DMA Channel Parameters

The first step in programming the DMA Unit is to set up the parameters for each channel.

10.2.1.1 Programming the Source and Destination Pointers

The following parameters are programmable for the source and destination pointers:

• pointer address

• address space (memory or I/O)

• automatic pointer indexing (increment, decrement or no change) after transfer

Channel

Priority

Synch

Both Requests Asserted

0

Low

SRC

1

Low

SRC

Channel

Priority

Synch

0

High

SRC

1

Low

SRC

Channel

Priority

Synch

0

High

Dest

1

Low

SRC

Channel 1 Channel 0 Channel 1 Channel 0

Channel 0 Channel 1 Channel 1

Channel 1 Channel 0 Channel 1

Channel 0

Channel 0

Channel 0 Completes

All Transfers

Destination Synch Releases Bus

Etc.

Etc.

Etc.

A1190-0A