8-27

INTERRUPT CONTROL UNIT

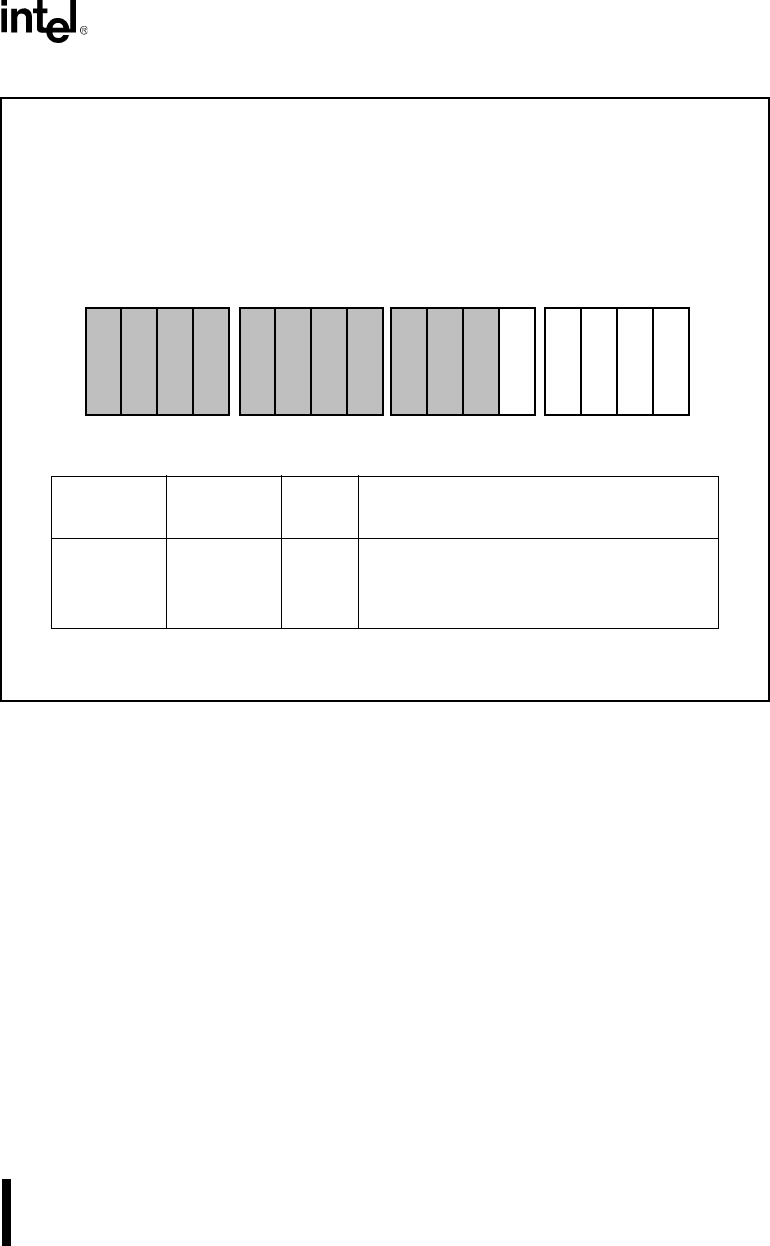

Figure 8-17. Interrupt Vector Register (Slave Mode Only)

8.5.1.2 End-Of-Interrupt Register

The End-of-Interrupt (EOI) register has the same function in Slave mode as in Master mode.

However, non-specific EOI commands are not supported, so the NSPEC bit is omitted from the

register. Only specific EOI commands can be issued. To clear an In-Service bit in Slave mode,

write the three least-significant bits of the interrupt type (from Table 8-5) to the VT2:0 bits.

Register Name: Interrupt Vector Register (Slave Mode only)

Register Mnemonic: INTVEC

Register Function: Specifies the five most-significant bit of the interrupt

vector types for the internal interrupt sources

Bit

Mnemonic

Bit Name

Reset

State

Function

T4:0 Interrupt

Vector Type

Field

00000 Specifies the five most-significant bits of the

interrupt vector types for the internal interrupt

sources. The three least-significant bits are

fixed (see Table 8-5).

NOTE: Reserved register bits are shown with gray shading. Reserved bits must be written

to a logic zero to ensure compatibility with future Intel products.

A1196-A0

15 0

T

0

T

2

T

1

T

3

T

4