D-21

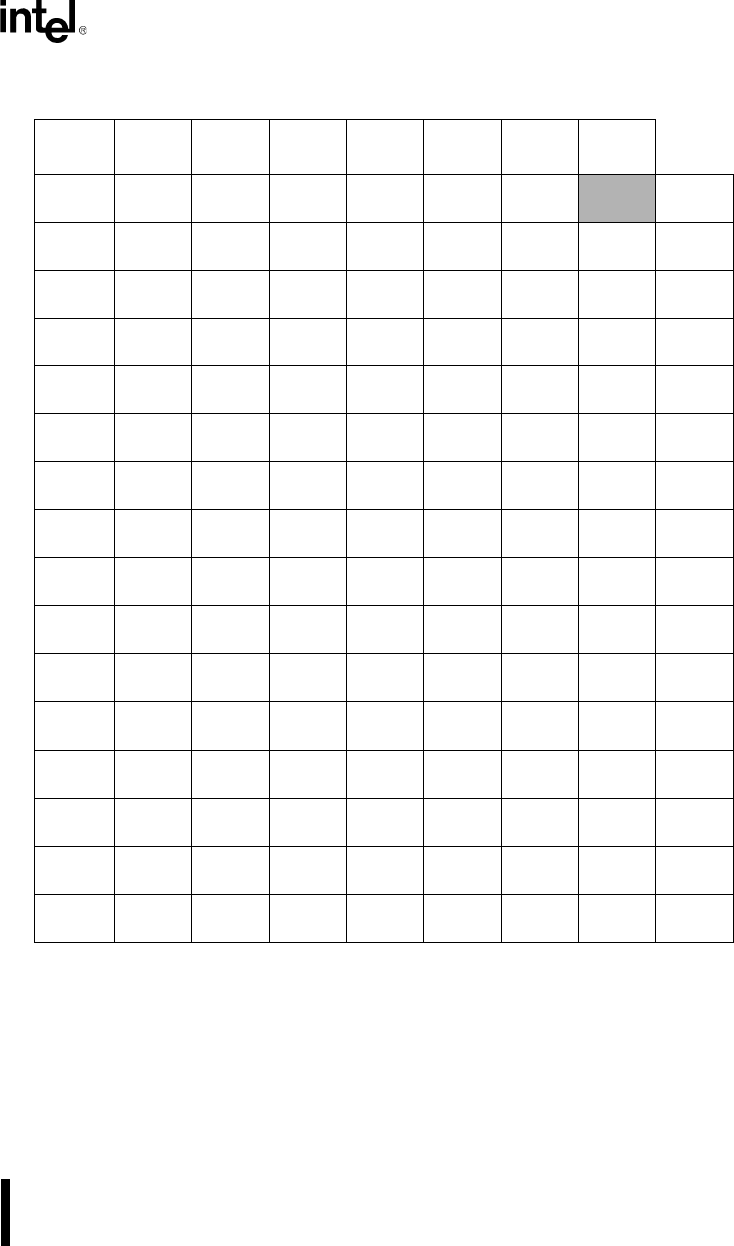

INSTRUCTION SET OPCODES AND CLOCK CYCLES

Table D-4. Mnemonic Encoding Matrix (Right Half)

x8 x9 xA xB xC xD xE xF

OR

b,f,r/m

OR

w,f,r/m

OR

b,t,r/m

OR

w,t,r/m

OR

b,i

OR

w,i

PUSH

CS

0x

SBB

b,f,r/m

SBB

w,f,r/m

SBB

b,t,r/m

SBB

w,t,r/m

SBB

b,i

SBB

w,i

PUSH

DS

POP

DS

1x

SUB

b,f,r/m

SUB

w,f,r/m

SUB

b,t,r/m

SUB

w,t,r/m

SUB

b,i

SUB

w,i

SEG

=CS

DAS

2x

CMP

b,f,r/m

CMP

w,f,r/m

CMP

b,t,r/m

CMP

w,t,r/m

CMP

b,i

CMP

w,i

SEG

=DS

AAS

3x

DEC

AX

DEC

CX

DEC

DX

DEC

BX

DEC

SP

DEC

BP

DEC

SI

DEC

DI

4x

POP

AX

POP

CX

POP

DX

POP

BX

POP

SP

POP

BP

POP

SI

POP

DI

5x

PUSH

w,i

IMUL

w,i

PUSH

b,i

IMUL

w,i

INS

b

INS

w

OUTS

b

OUTS

w

6x

JS JNS JP/

JPE

JNP/

JPO

JL/

JNGE

JNL/

JGE

JLE/

JNG

JNLE/

JG

7x

MOV

b,f,r/m

MOV

w,f,r/m

MOV

b,t,r/m

MOV

w,t,r/m

MOV

sr,f,r/m

LEA MOV

sr,t,r/m

POP

r/m

8x

CBW CWD CALL

L,D

WAIT PUSHF POPF SAHF LAHF

9x

TEST

b,ia

TEST

w,ia

STOS STOS LODS LODS SCAS SCAS

Ax

MOV

i→AX

MOV

i→CX

MOV

i→DX

MOV

i→BX

MOV

i→SP

MOV

i→BP

MOV

i→SI

MOV

i→DI

Bx

ENTER LEAVE RET

l(i+SP)

RET

l

INT

type 3

INT

(any)

INTO IRET

Cx

ESC

0

ESC

1

ESC

2

ESC

3

ESC

4

ESC

5

ESC

6

ESC

7

Dx

CALL JMP JMP JMP IN IN OUT OUT

Ex

CLC STC CLI STI CLS STD Grp2

b,r/m

Grp2

w,r/m

Fx

NOTE: Table D-5 defines abbreviations used in this matrix. Shading indicates reserved opcodes.