OVERVIEW OF THE 80C186 FAMILY ARCHITECTURE

2-40

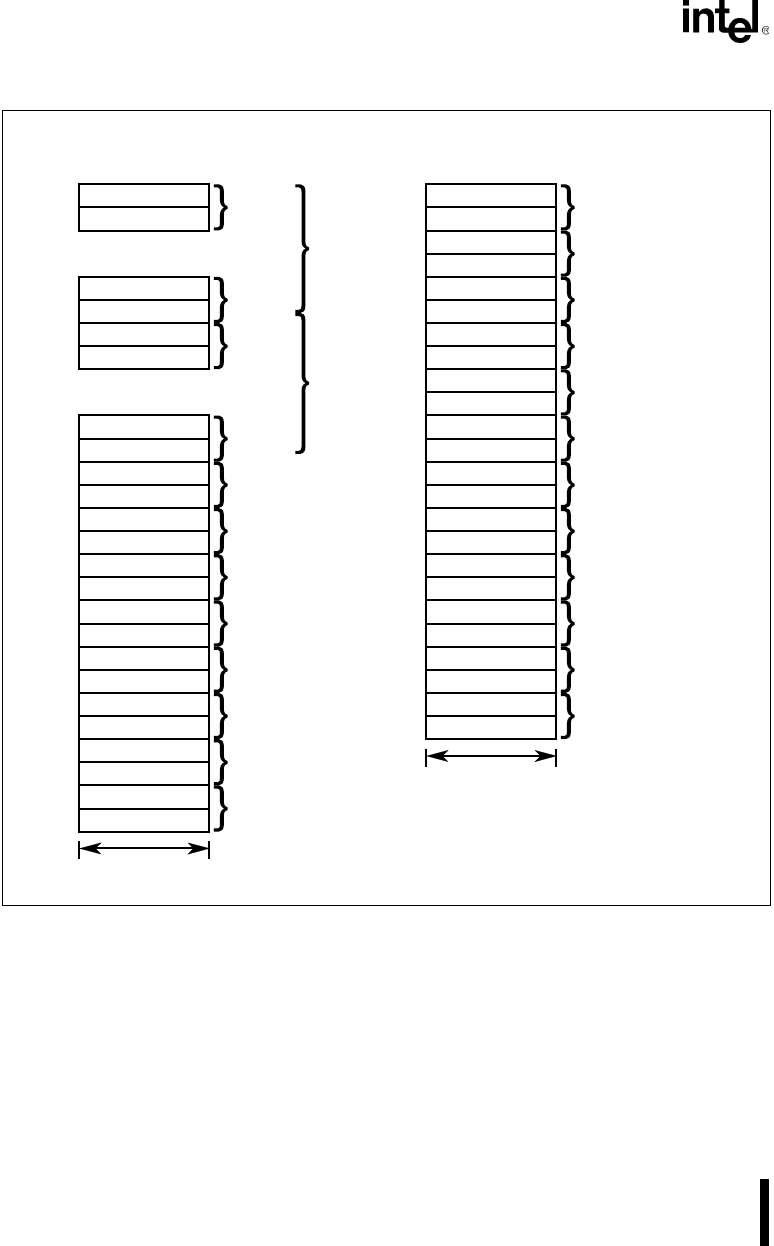

Figure 2-25. Interrupt Vector Table

When an interrupt is acknowledged, a common event sequence (Figure 2-26) allows the proces-

sor to execute the interrupt service routine.

1. The processor saves a partial machine status by pushing the Processor Status Word onto

the stack.

Memory

Address

Table

Entry

Vector

Definition

Type 255

User

Available

Reserved

Type 32

Type 31

CS =Code Segment Value

IP = Instruction Pointer Value

Type 20

2 Bytes

3FE

3FC

82

80

7E

7C

52

50

4E

4C

4A

48

46

44

42

40

3E

3C

3A

38

36

34

32

30

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

Type 11 - DMA1

2E

2C

2A

28

26

24

22

20

1E

1C

1A

18

16

14

12

10

0E

0C

0A

08

06

04

02

00

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

CS

IP

2 Bytes

Type 19 - Timer 2

Type 18 - Timer 1

Type 17 - Reserved

Type 16 - Numerics

Type 15 - INT3

Type 14 - INT2

Type 10 - DMA0

Type 9 - Reserved

Type 8 - Timer 0

Type 7 - ESC Opcode

Type 6 - Unused

Opcode

Type 5 - Array

Bounds

Type 4 - Overflow

Type 3 - Breakpoint

Type 2 - NMI

Type 1 - Single-Step

Type 0 - Divide Error

Memory

Address

Table

Entry

Vector

Definition

Type 13 - INT1

Type 12 - INT0

A1009-02