8-21

INTERRUPT CONTROL UNIT

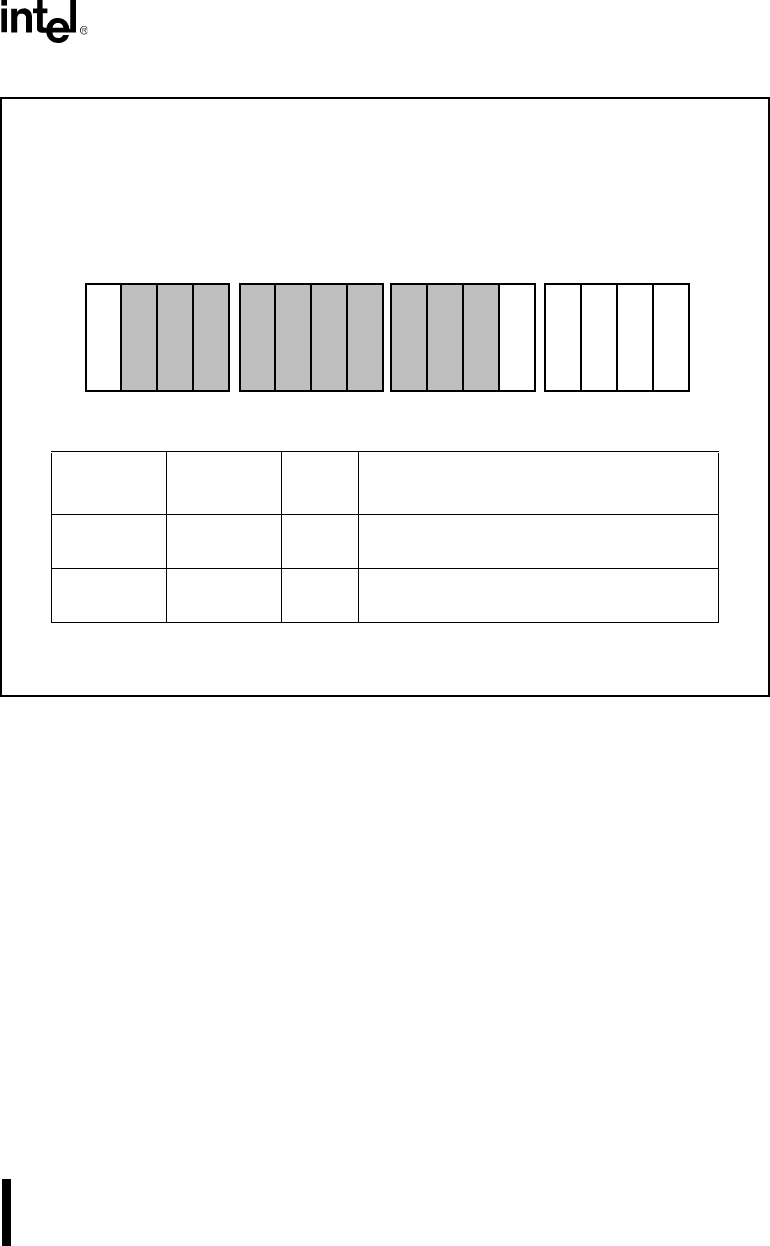

Figure 8-12. Poll Status Register

8.4.7 End-of-Interrupt (EOI) Register

The End-of-Interrupt register (Figure 8-13) issues an End-of-Interrupt (EOI) command to the In-

terrupt Control Unit, which clears the In-Service bit for the associated interrupt. An interrupt han-

dler typically ends with an EOI command. There are two types of EOI commands: nonspecific

and specific. A nonspecific EOI simply clears the In-Service bit of the highest priority interrupt.

To issue a nonspecific EOI command, set the NSPEC bit. (Write 8000H to the EOI register.)

A specific EOI clears a particular In-Service bit. To issue a specific EOI command, clear the

NSPEC bit and write the VT4:0 bits with the interrupt type of the interrupt whose In-Service bit

you wish to clear. For example, to clear the In-Service bit for INT2, write 000EH to the EOI reg-

ister. The timer interrupts share an In-Service bit. To clear the In-Service bit for any timer inter-

rupt with a specific EOI, write 0008H (interrupt type 8) to the EOI register.

Register Name: Poll Status Register

Register Mnemonic: POLLSTS

Register Function: Read to check for pending interrupts when polling

Bit

Mnemonic

Bit Name

Reset

State

Function

IREQ Interrupt

Request

0 This bit is set to indicate a pending interrupt.

VT4:0 Vector Type 0 Contains the interrupt type of the highest

priority pending interrupt.

NOTE: Reserved register bits are shown with gray shading. Reserved bits must be written

to a logic zero to ensure compatibility with future Intel products.

A1209-A0

15 0

V

T

0

V

T

2

V

T

3

V

T

4

I

R

E

Q

V

T

1