CHIP-SELECT UNIT

6-2

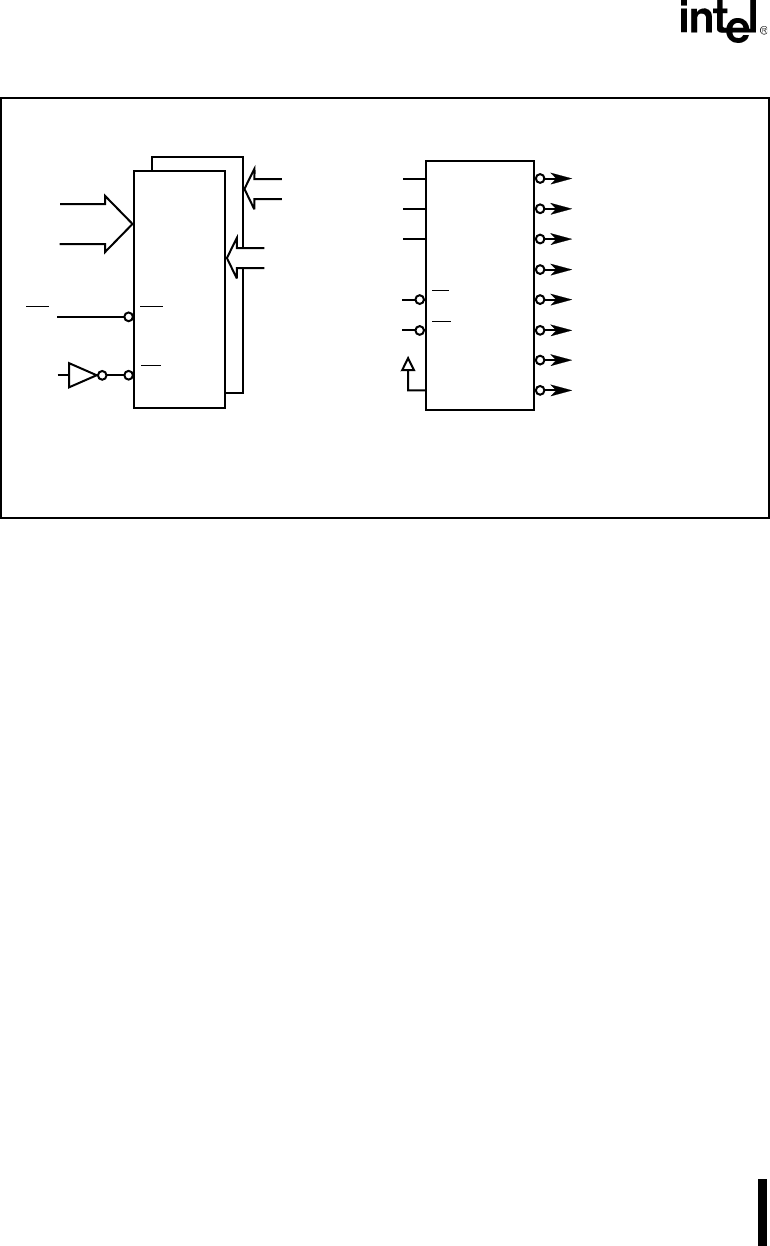

Figure 6-1. Common Chip-Select Generation Methods

6.3 CHIP-SELECT UNIT FUNCTIONAL OVERVIEW

The Chip-Select Unit (CSU) decodes bus cycle address and status information and enables the

appropriate chip-select. Figure 6-3 illustrates the timing of a chip-select during a bus cycle. Note

that the chip-select goes active in the same bus state as address goes active, eliminating any delay

through address latches and decoder circuits. The Chip-Select Unit activates a chip-select for bus

cycles initiated by the CPU, DMA Control Unit or Refresh Control Unit.

Six of the chip-selects map only into memory address space, while the remaining seven can map

into either memory or I/O address space. The chip-selects typically associate with memory and

peripheral devices as follows:

27C256

A1:13

A16

A0:12

D15:8

(A)

RD

CS

Chip-Selects Using

Addresses Directly

(B)

HLDA

74AC138

E3

ALE

A19

A18

A17

A3

A2

A1

E1

E2

Selects 768K to 896K

Selects 896K to 1M

Selects 128K to 256K

Selects 0 to 128K

Chip-Selects Using

Simple Decoder

OE

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

D7:0

A1168-0A