2-5

OVERVIEW OF THE 80C186 FAMILY ARCHITECTURE

The data registers can be addressed by their upper or lower halves. Each data register can be used

interchangeably as a 16-bit register or two 8-bit registers. The pointer registers are always access-

ed as 16-bit values. The CPU can use data registers without constraint in most arithmetic and log-

ic operations. Arithmetic and logic operations can also use the pointer and index registers. Some

instructions use certain registers implicitly (see Table 2-1), allowing compact encoding.

The contents of the general-purpose registers are undefined following a processor reset.

2.1.4 Segment Registers

The 80C186 Modular Core family memory space is 1 Mbyte in size and divided into logical seg-

ments of up to 64 Kbytes each. The CPU has direct access to four segments at a time. The segment

registers contain the base addresses (starting locations) of these memory segments (see Figure

2-4). The CS register points to the current code segment, which contains instructions to be

fetched. The SS register points to the current stack segment, which is used for all stack operations.

The DS register points to the current data segment, which generally contains program variables.

The ES register points to the current extra segment, which is typically used for data storage. The

CS register initializes to 0FFFFH, and the SS, DS and ES registers initialize to 0000H. Programs

can access and manipulate the segment registers with several instructions.

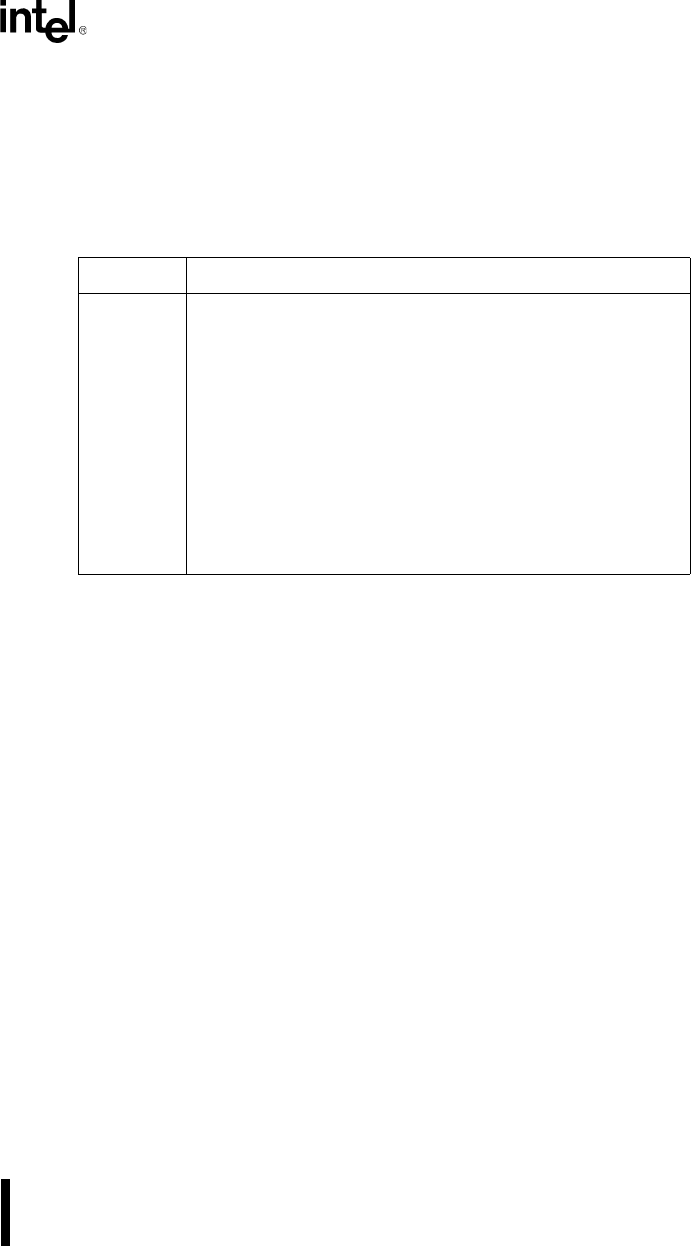

Table 2-1. Implicit Use of General Registers

Register Operations

AX Word Multiply, Word Divide, Word I/O

AL Byte Multiply, Byte Divide, Byte I/O, Translate, Decimal Arithmetic

AH Byte Multiply, Byte Divide

BX Translate

CX String Operations, Loops

CL Variable Shift and Rotate

DX Word Multiply, Word Divide, Indirect I/O

SP Stack Operations

SI String Operations

DI String Operations