C-39

INSTRUCTION SET DESCRIPTIONS

ROR Rotate Right:

ROR

dest, count

Operates similar to ROL except that

the bits in the destination byte or word

are rotated right instead of left.

Instruction Operands:

ROR reg, n

ROR mem, n

ROR reg, CL

ROR mem, CL

(temp) ← count

do while (temp) ≠ 0

(CF) ← low-order bit of (dest)

(dest) ← (dest) / 2

high-order bit of (dest) ← (CF)

(temp) ← (temp) – 1

if

count = 1

then

if

high-order bit of (dest) ≠

next-to-high-order bit of (dest)

then

(OF) ← 1

else

(OF) ← 0

else

(OF) undefined

AF –

CF

DF –

IF –

OF

PF –

SF –

TF –

ZF –

SAHF Store Register AH Into Flags:

SAHF

Transfers bits 7, 6, 4, 2, and 0 from

register AH into SF, ZF, AF, PF, and CF,

respectively, replacing whatever

values these flags previously had.

Instruction Operands:

none

(SF):(ZF):X:(AF):X:(PF):X:(CF) ← (AH) AF

CF

DF –

IF –

OF –

PF

SF

TF –

ZF

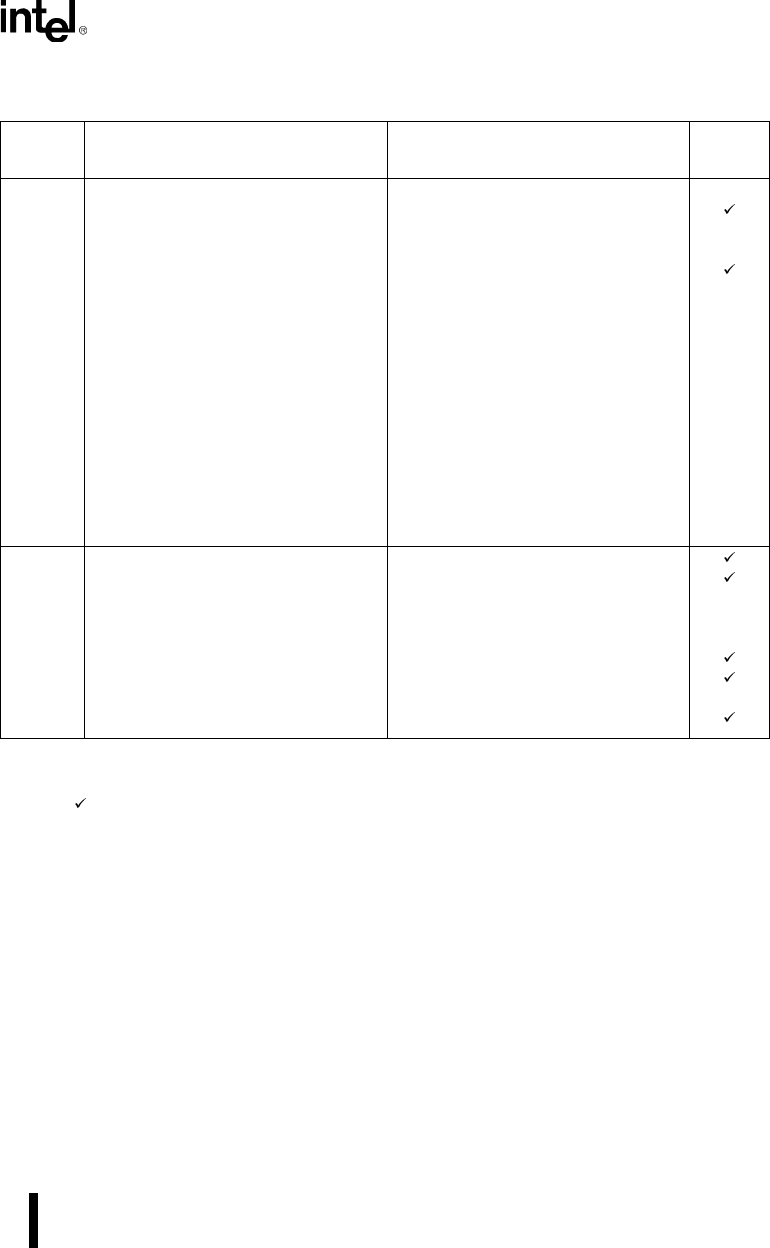

Table C-4. Instruction Set (Continued)

Name Description Operation

Flags

Affected

NOTE: The three symbols used in the Flags Affected column are defined as follows:

– the contents of the flag remain unchanged after the instruction is executed

? the contents of the flag is undefined after the instruction is executed

the flag is updated after the instruction is executed