BUS INTERFACE UNIT

3-18

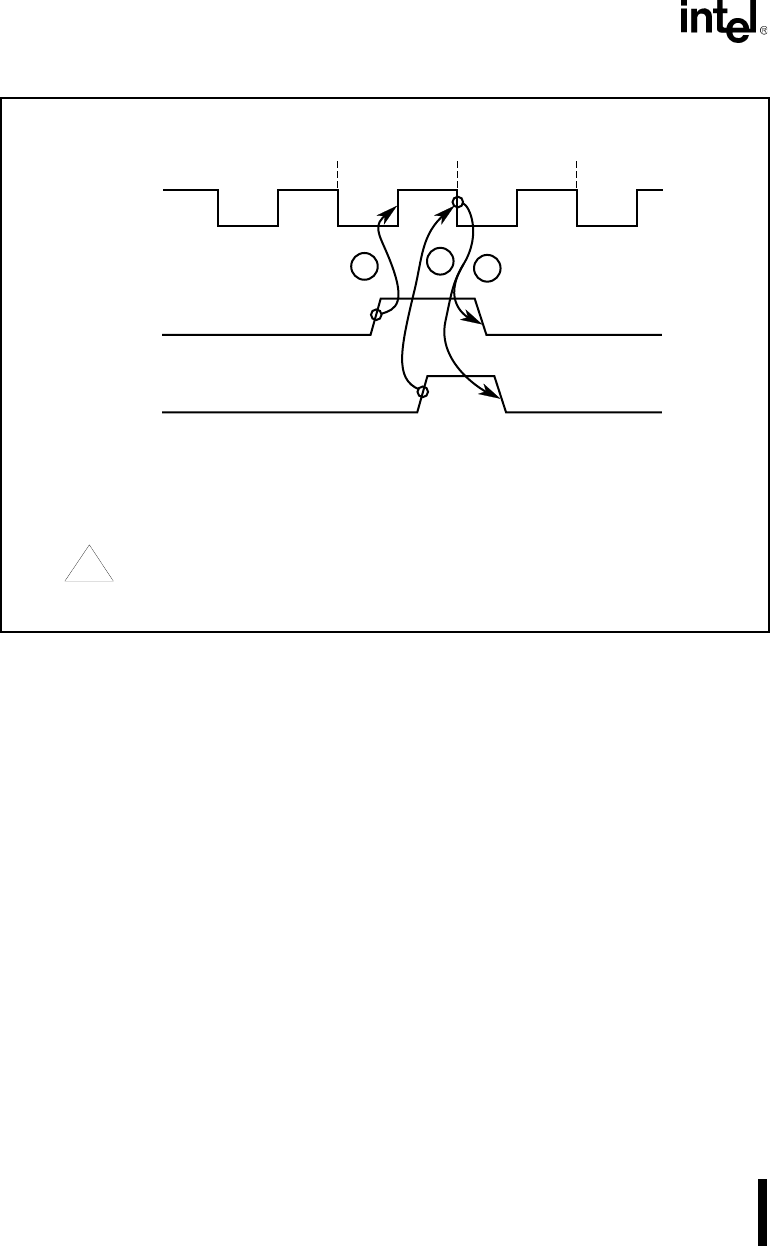

Figure 3-17. Normally Not-Ready System Timing

A valid not-ready input can be generated as late as phase 1 of T3 to insert wait states in a normally

ready system. A normally not-ready system must run wait states if the not-ready condition cannot

be met in time. Figure 3-18 illustrates the minimum and maximum timing necessary to insert wait

states in a normally ready system. Figure 3-18 also shows how to terminate a bus cycle with wait

states in a normally ready system.

The BIU can execute an indefinite number of wait states. However, bus cycles with large numbers

of wait states limit the performance of the CPU and the integrated peripherals. CPU performance

suffers because the instruction prefetch queue cannot be kept full. Integrated peripheral perfor-

mance suffers because the maximum bus bandwidth decreases.

3.4.4 Idle States

Under most operating conditions, the BIU executes consecutive (back-to-back) bus cycles. How-

ever, several conditions cause the BIU to become idle. An idle condition occurs between bus cy-

cles (see Figure 3-8 on page 3-9) and may last an indefinite period of time, depending on the

instruction sequence.

ARDY

CLKOUT

T2

or T3

or TW

T4

In a Normally-Not-Ready system, wait states are inserted until (1 or 2) and 3 are met.

1. T

ARYCH

: ARDY active to clock high (assumes ARDY remains active until 3).

2. T

SRYCL

: SRDY active to clock low.

3. T

CLARX,

T

CLSRY

: ARDY and SRDY hold from clock low.

1

2

SRDY

3

!

Failure to meet SRDY setup and hold can cause a device failure

(i.e., the bus hangs or operates inappropriately).

T3

or TW

A1511-0A