4-48 Registers

Register: 0x14

Interrupt Status Zero (ISTAT0)

Read/Write

This register is accessible by the host CPU while a LSI53C875A is

executing SCRIPTS (without interfering in the operation of the function).

It is used to poll for interrupts if hardware interrupts are disabled. Read

this register after servicing an interrupt to check for stacked interrupts.

ABRT Abort Operation 7

Setting this bit aborts the current operation under

execution by the LSI53C875A. If this bit is set and an

interrupt is received, clear this bit before reading the DMA

Status (DSTAT) register to prevent further aborted

interrupts from being generated. The sequence to abort

any operation is:

1. Set this bit.

2. Wait for an interrupt.

3. Read the Interrupt Status Zero (ISTAT0) and

Interrupt Status One (ISTAT1) registers.

4. If the SCSI Interrupt Pending bit is set, then read the

SCSI Interrupt Status Zero (SIST0) or SCSI Interrupt

Status One (SIST1) register to determine the cause

oftheSCSIInterruptandgobacktoStep2.

5. If the SCSI Interrupt Pending bit is clear, and the

DMA Interrupt Pending bit is set, then write 0x00

value to this register.

6. Read the DMA Status (DSTAT) register to verify the

aborted interrupt and to see if any other interrupting

conditions have occurred.

SRST Software Reset 6

Setting this bit resets the LSI53C875A. All operating

registers are cleared to their respective default values

and all SCSI signals are deasserted. Setting this bit does

not assert the SCSI RST/ signal. This reset does not

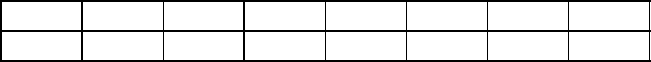

76543210

ABRT SRST SIGP SEM CON INTF SIP DIP

00000000