SCSI Functional Description 2-35

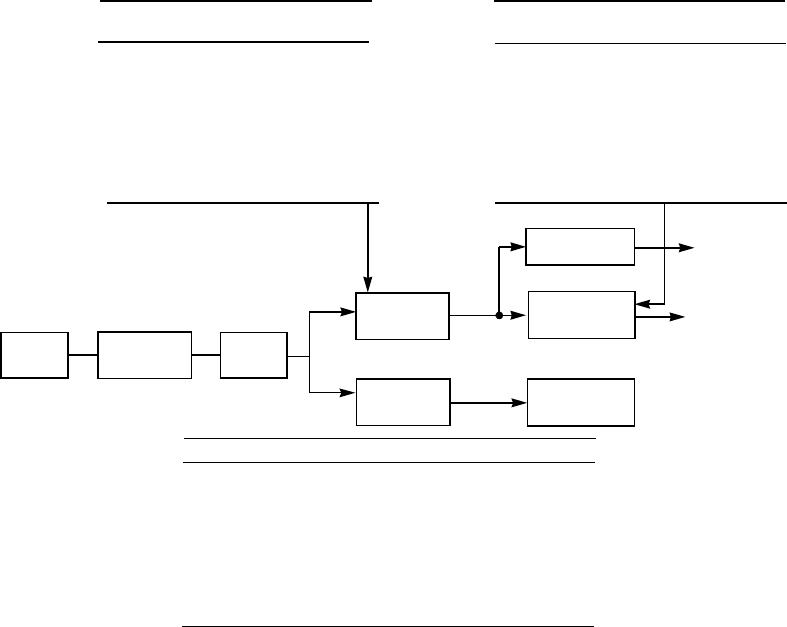

Figure 2.6 Determining the Synchronous Transfer Rate

SCLK

Clock

Quadrupler

QCLK

SCF

Divider

CCF

Divider

Synchronous

Divider

Asynchronous

SCSI Logic

Divide by 4

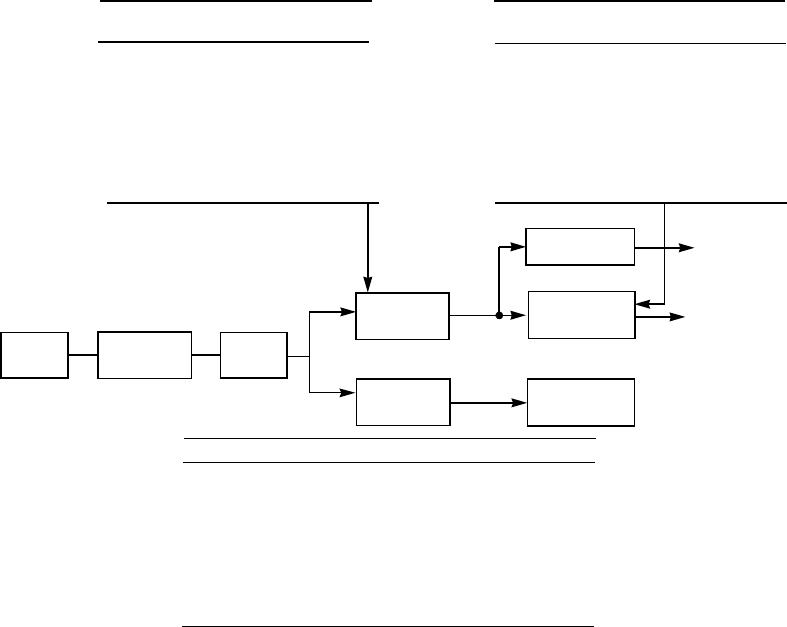

SCF2 SCF1 SCF0 SCF

Divisor

0011

0101.5

0112

1003

0003

1014

1106

1118

TP2 TP1 TP0 XFERP

Divisor

0004

0015

0106

0117

1008

1019

11010

11111

CCF2 CCF1 CCF0 Divisor QCLK (MHz)

0 0 1 1 50.1–66.00

0 1 0 1.5 16.67–25.00

0 1 1 2 25.1–37.50

1 0 0 3 37.51–50.00

0 0 0 3 50.01–66.00

1 0 1 4 75.01–80.00

1 1 0 6 120

1 1 1 8 160

Example 1 (using 40 MHz clock)

QCLK (Quadrupled SCSI Clock) = 160 MHz

SCF = 1 (/1), XFERP = 4 (/8), CCF = 7 (/8)

Synchronous send rate = (QCLK/SCF)/XFERP =

(160/1) /8

1

= 20 Mbytes/s

Synchronous receive rate = (QCLK/SCF) /4 =

(160/1) /4

2

= 40 Mbytes/s

This point

must not

exceed

160 MHz

Receive

Clock

Send Clock

(to SCSI Bus)

This point must

not exceed 20 MHz.

SCLK = 40 MHz

Example 2 (using 20 MHz clock)

QCLK (Quadrupled SCSI Clock) = 80 MHz

SCF = 1 (/1), XFERP = 0 (/4), CCF = 5 (/4)

Synchronous send rate = (QCLK/SCF)/XFERP =

(80/1) /4 = 20 Mbytes/s

Synchronous receive rate = (QCLK/SCF) /4 =

(80/1) /4 = 20 Mbytes/s

SCLK = 20 MHz

Note:

• Synchronous send rate must not exceed 20 Mbytes/s because the

LSI53C875A is an Ultra SCSI device.

• Although maximum synchronous receive rate is 40 Mbytes/s the

maximum transfer rate is 20 Mbytes/s because the LSI53C875A is an

Ultra SCSI device.