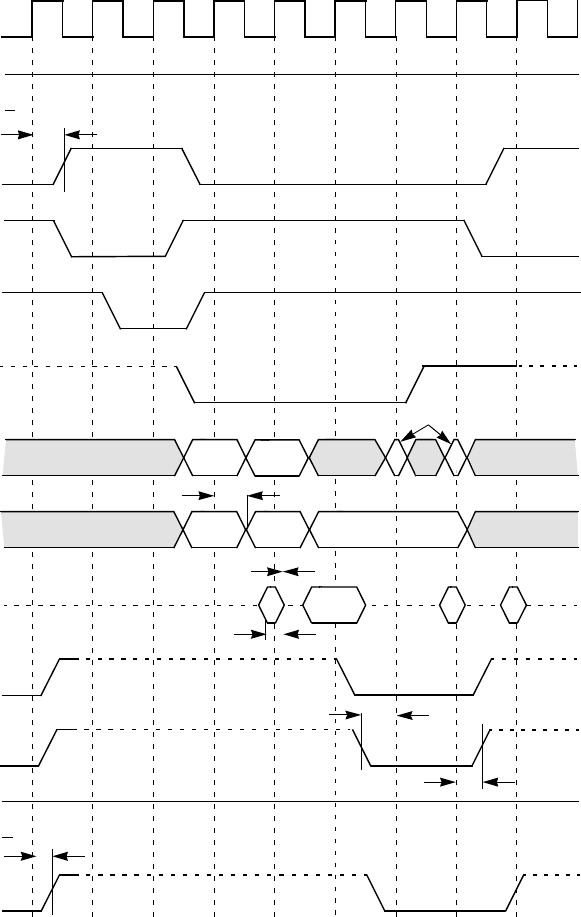

6-30 Electrical Specifications

Figure 6.20 Burst Read, 64-Bit Address and Data

t

1

t

2

CLK

GPIO0_FETCH/

(Driven by LSI53C875A)

GPIO1_MASTER/

(Driven by LSI53C875A)

REQ/

(Driven by LSI53C875A)

PAR

(Addr drvn by LSI53C875A;

IRDY/

(Driven by LSI53C875A)

TRDY/

(Driven by Target)

STOP/

(Driven by Target)

DEVSEL/

(Driven by Target)

AD[31:0]

(Addr driven by LSI53C875A-

C_BE[3:0]/

(Driven by LSI53C875A)

t

3

GNT/

(Driven by Arbiter)

FRAME/

(Driven by LSI53C875A)

Addr

Out Lo

t

2

Data driven by Target)

Data drvn by Target)

BE

t

1

Data In

In Out In

In

t

10

BusDual

Addr CMD

t

2

Addr

Out Hi