Memory Move Instructions 5-33

• Indirect addresses are not allowed. A burst of data is fetched from

the source address, put into the DMA FIFO and then written out to

the destination address. The move continues until the byte count

decrements to zero, then another SCRIPTS is fetched from system

memory.

The DMA SCRIPTS Pointer Save (DSPS) and Data Structure Address

(DSA) registers are additional holding registers used during the Memory

Move. However, the contents of the Data Structure Address (DSA)

register are preserved.

5.7.1 First Dword

IT[2:0] Instruction Type - Memory Move [31:29]

The IT bit configuration (110) defines a Memory Move

Instruction Type.

R Reserved [28:25]

These bits are reserved and must be zero. If any of these

bits are set, an illegal instruction interrupt occurs.

NF No Flush 24

When this bit is set, the LSI53C875A performs a Memory

Move without flushing the prefetch unit. When this bit is

cleared, the Memory Move instruction automatically

flushes the prefetch unit. Use the No Flush option if the

source and destination are not within four instructions of

the current Memory Move instruction.

Note:

This bit has no effect unless the Prefetch Enable bit in the

DMA Control (DCNTL) register is set. For information on

SCRIPTS instruction prefetching, see Chapter 2.

TC[23:0] Transfer Counter [23:0]

The number of bytes to transfer is stored in the lower

24 bits of the first instruction word.

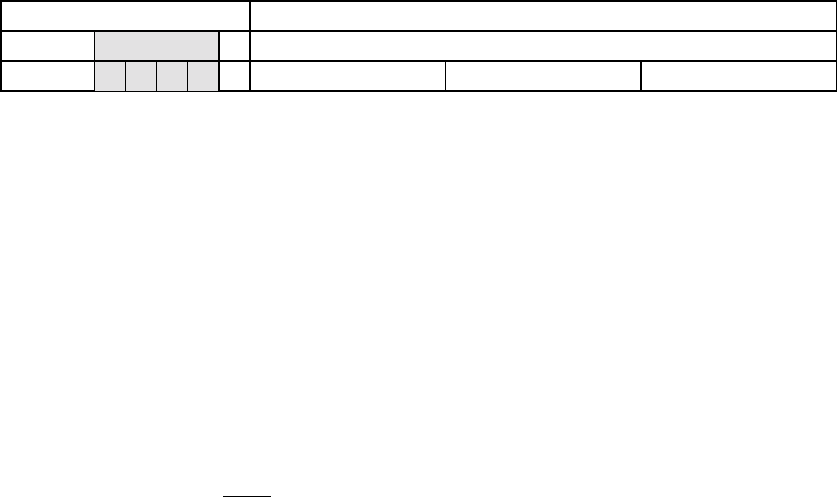

31 29 28 25 24 23 0

DMA Command (DCMD) Register DMA Byte Counter (DBC) Register

IT[2:0]

R NF Transfer Counter (TC) [23:0]

110

0 0 0 0 x xxxxxxxxxxxxxxxxxxxxxxxx