4-66 Registers

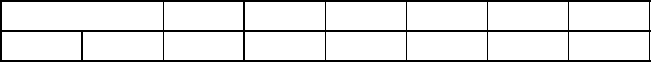

Register: 0x38

DMA Mode (DMODE)

Read/Write

BL[1:0] Burst Length [7:6]

These bits control the maximum number of Dwords

transferred per bus ownership, regardless of whether the

transfers are back-to-back, burst, or a combination of

both. The LSI53C875A asserts the Bus Request (REQ/)

output when the DMA FIFO can accommodate a transfer

of at least one burst threshold of data. Bus Request

(REQ/) is also asserted during start-of-transfer and

end-of-transfer cleanup and alignment, even if less than

a full burst of transfers is performed. The LSI53C875A

inserts a “fairness delay” of four CLKs between burst

transfers (as set in BL[2:0]) during normal operation. The

fairness delay is not inserted during PCI retry cycles. This

gives the CPU and other bus master devices the

opportunity to access the PCI bus between bursts.

The LSI53C875A will only support burst thresholds of up

to 16 Dwords in the small FIFO mode. Setting the burst

threshold to higher than 16 Dwords in the small FIFO

mode will yield unexpected results in burst lengths. The

big FIFO mode is activated by setting bit 5 of the Chip

Test Five (CTEST5) register. In the big FIFO mode, the

LSI53C875A will support burst thresholds of up to

128 Dwords.

76543210

BL[1:0] SIOM DIOM ERL ERMP BOF MAN

00000000