SCSI Registers 4-91

Register: 0x4F

SCSI Test Three (STEST3)

Read/Write

TE TolerANT Enable 7

Setting this bit enables the active negation portion of

LSI Logic TolerANT technology. Active negation causes

the SCSI Request, Acknowledge, Data, and Parity

signals to be actively deasserted, instead of relying on

external pull-ups, when the LSI53C875A is driving these

signals. Active deassertion of these signals occurs only

when the LSI53C875A is in an information transfer

phase. When operating in a differential environment or at

fast SCSI timings, TolerANT Active negation should be

enabled to improve setup and deassertion times. Active

negation is disabled after reset or when this bit is cleared.

For more information on LSI Logic TolerANT technology,

see Chapter 1, “General Description.”

Note:

Set this bit if the Enable Ultra SCSI bit in SCSI Control

Three (SCNTL3) is set.

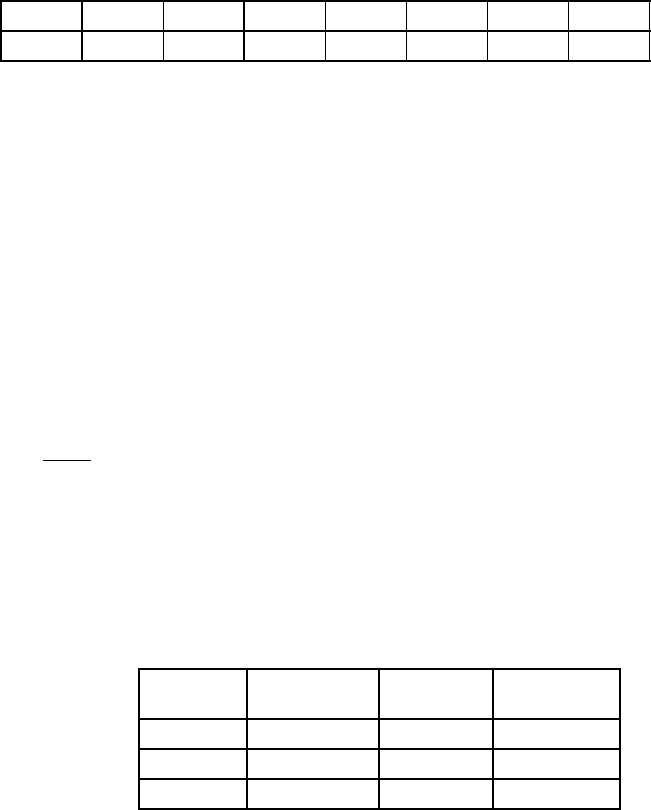

STR SCSI FIFO Test Read 6

Setting this bit places the SCSI core into a test mode in

which the SCSI FIFO is easily read. Reading the least

significant byte of the SCSI Output Data Latch (SODL)

register causes the FIFO to unload. The functions are

summarized in the table below.

HSC Halt SCSI Clock 5

Asserting this bit causes the internal divided SCSI clock

to come to a stop in a glitchless manner. This bit is used

76543210

TE STR HSC DSI S16 TTM CSF STW

0000x000

Register

Name

Register

Operation FIFO Bits

FIFO

Function

SODL Read [15:0] Unload

SODL0 Read [7:0] Unload

SODL1 Read [15:8] None