6-42 Electrical Specifications

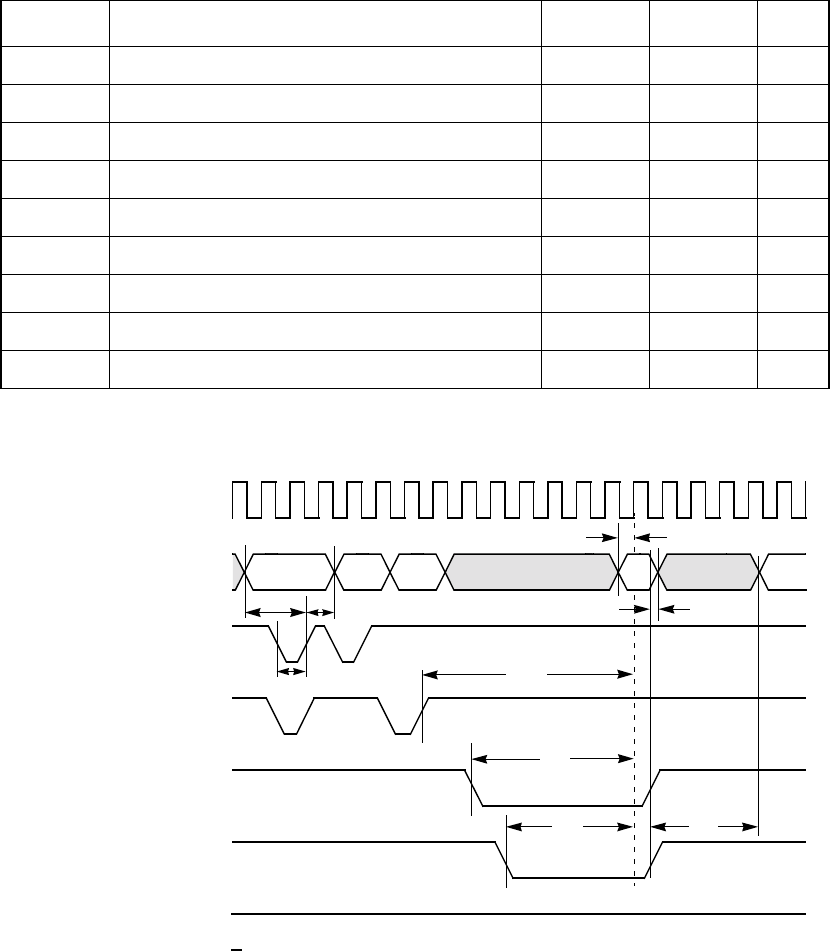

Figure 6.25 Normal/Fast Memory (≥=128 Kbytes) Single Byte Access Read Cycle

Table 6.31 Normal/Fast Memory (

≥=128 Kbytes) Single Byte Access Read Cycle

Symbol Parameter Min Max Unit

t

11

Address setup to MAS/ HIGH 25 – ns

t

12

Address hold from MAS/ HIGH 15 – ns

t

13

MAS/ pulse width 25 – ns

t

14

MCE/ LOW to data clocked in 150 – ns

t

15

Address valid to data clocked in 205 – ns

t

16

MOE/ LOW to data clocked in 100 – ns

t

17

Data hold from address, MOE/, MCE/ change 0 – ns

t

18

Address out from MOE/, MCE/ HIGH 50 – ns

t

19

Data setup to CLK HIGH 5 – ns

CLK

MAD

(Addr driven by LSI53C875A;

Data driven by memory)

MAS1/

(Driven by LSI53C875A)

MAS0/

(Driven by LSI53C875A)

MCE/

(Driven by LSI53C875A)

MOE/

(Driven by LSI53C875A)

MWE/

(Driven by LSI53C875A)

t

11

t

12

t

13

t

15

t

14

t

16

t

18

t

17

t

19

Higher

Address

1. 2.

3.

1. Middle Address 2. Lower Address 3. Valid Read Data