5-36 SCSI SCRIPTS Instruction Set

The SIOM and DIOM bits in the DMA Mode (DMODE) register determine

whether the destination or source address of the instruction is in Memory

space or I/O space, as illustrated in the following table. The Load and

Store utilizes the PCI commands for I/O read and I/O write to access the

I/O space.

5.8.1 First Dword

IT[2:0] Instruction Type [31:29]

These bits should be 0b111, indicating the Load and

Store instruction.

DSA DSA Relative 28

When this bit is cleared, the value in the DMA SCRIPTS

Pointer Save (DSPS) is the actual 32-bit memory address

used to perform the Load and Store to/from. When this

bit is set, the chip determines the memory address to

perform the Load and Store to/from by adding the 24-bit

signed offset value in the DMA SCRIPTS Pointer Save

(DSPS) to the Data Structure Address (DSA).

R Reserved [27:26]

NF No Flush (Store instruction only) 25

When this bit is set, the LSI53C875A performs a Store

without flushing the prefetch unit. When this bit is cleared,

the Store instruction automatically flushes the prefetch

unit. Use No Flush if the source and destination are not

within four instructions of the current Store instruction.

This bit has no effect on the Load instruction.

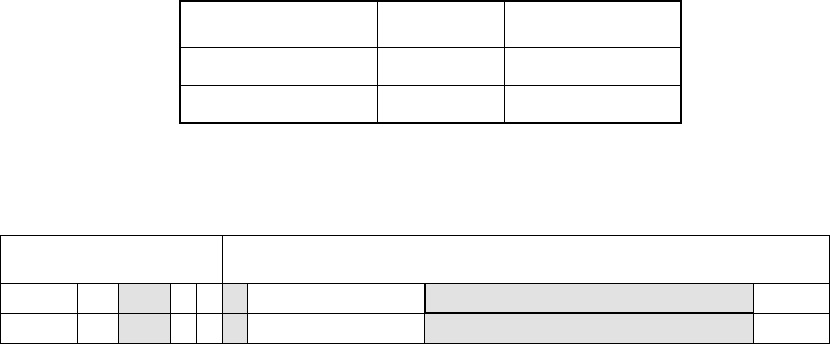

Bit Source Destination

SIOM (Load) Memory Register

DIOM (Store) Register Memory

31 29 28 27 26 25 24 23 22 16 15 3 2 0

DMA Command (DCMD)

Register

DMA Byte Counter (DBC) Register

IT[2:0] DSA

RNFLSR RA[6:0] RBC

111 x

0 0xx0xxxxxxx0 0 0 0 0 0 0 0 0 0 0 0 0xxx