Flash Memory Operation

5-7

Flash Memory Controller

Initiating an Erase from RAM

Any erase cycle may be initiated from RAM. In this case, the CPU is not held

and can continue to execute code from RAM. The BUSY bit must be polled to

determine the end of the erase cycle before the CPU can access any flash

address again. If a flash access occurs while BUSY=1, it is an access violation,

ACCVIFG will be set, and the erase results will be unpredictable.

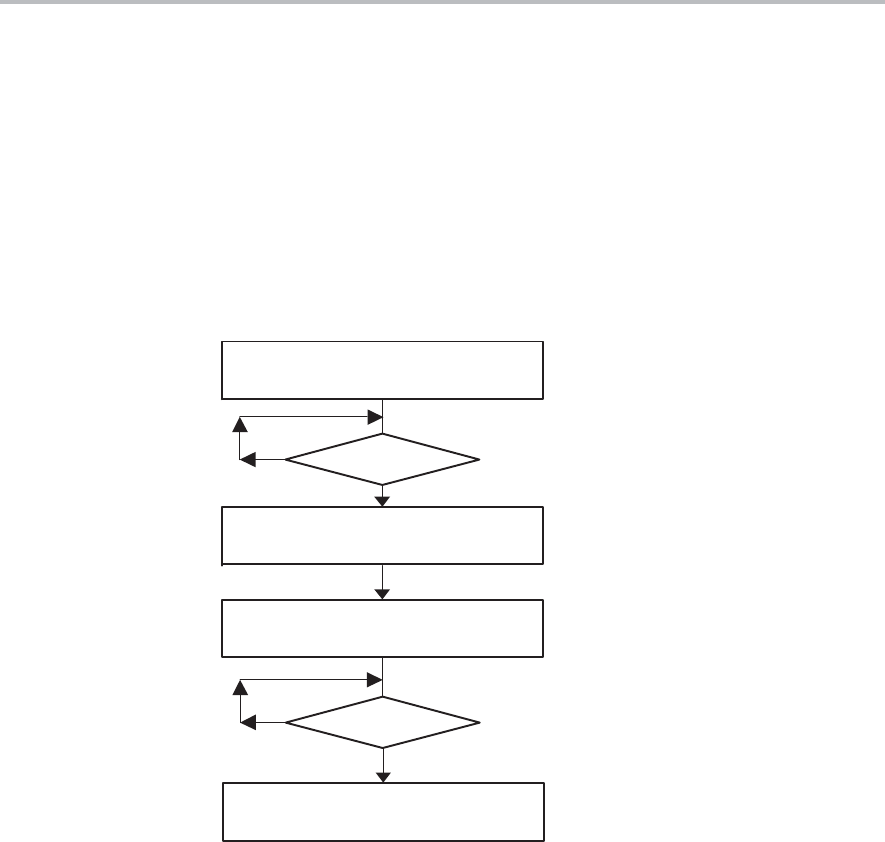

The flow to initiate an erase from flash from RAM is shown in Figure 5−6.

Figure 5−6. Erase Cycle from Within RAM

yes

BUSY = 1

yes

BUSY = 1

Disable all interrupts and watchdog

Setup flash controller and

erase mode

Dummy write

Set LOCK = 1, re-enable

interrupts and watchdog

; Segment Erase from RAM. 514 kHz < SMCLK < 952 kHz

; Assumes ACCVIE = NMIIE = OFIE = 0.

MOV #WDTPW+WDTHOLD,&WDTCTL ; Disable WDT

DINT ; Disable interrupts

L1 BIT #BUSY,&FCTL3 ; Test BUSY

JNZ L1 ; Loop while busy

MOV #FWKEY+FSSEL1+FN0,&FCTL2 ; SMCLK/2

MOV #FWKEY,&FCTL3 ; Clear LOCK

MOV #FWKEY+ERASE,&FCTL1 ; Enable erase

CLR &0FC10h ; Dummy write, erase S1

L2 BIT #BUSY,&FCTL3 ; Test BUSY

JNZ L2 ; Loop while busy

MOV #FWKEY+LOCK,&FCTL3 ; Done, set LOCK

... ; Re-enable WDT?

EINT ; Enable interrupts