Timer_A Operation

11-17

Timer_A

11.2.6 Timer_A Interrupts

Two interrupt vectors are associated with the 16-bit Timer_A module:

- TACCR0 interrupt vector for TACCR0 CCIFG

- TAIV interrupt vector for all other CCIFG flags and TAIFG

In capture mode any CCIFG flag is set when a timer value is captured in the

associated TACCRx register. In compare mode, any CCIFG flag is set if TAR

counts to the associated TACCRx value. Software may also set or clear any

CCIFG flag. All CCIFG flags request an interrupt when their corresponding

CCIE bit and the GIE bit are set.

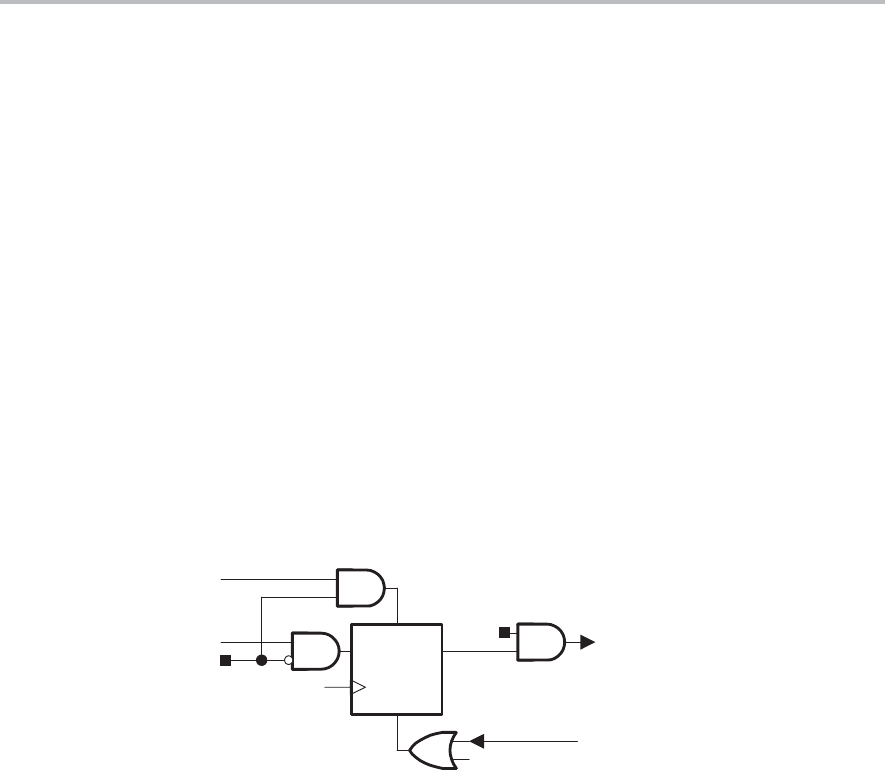

TACCR0 Interrupt

The TACCR0 CCIFG flag has the highest Timer_A interrupt priority and has

a dedicated interrupt vector as shown in Figure 11−15. The TACCR0 CCIFG

flag is automatically reset when the TACCR0 interrupt request is serviced.

Figure 11−15.Capture/Compare TACCR0 Interrupt Flag

D

Set

Q

IRQ, Interrupt Service Requested

Reset

Timer Clock

POR

CAP

EQU0

Capture

IRACC, Interrupt Request Accepted

CCIE

TAIV, Interrupt Vector Generator

The TACCR1 CCIFG, TACCR2 CCIFG, and TAIFG flags are prioritized and

combined to source a single interrupt vector. The interrupt vector register TAIV

is used to determine which flag requested an interrupt.

The highest priority enabled interrupt generates a number in the TAIV register

(see register description). This number can be evaluated or added to the

program counter to automatically enter the appropriate software routine.

Disabled Timer_A interrupts do not affect the TAIV value.

Any access, read or write, of the TAIV register automatically resets the highest

pending interrupt flag. If another interrupt flag is set, another interrupt is

immediately generated after servicing the initial interrupt. For example, if the

TACCR1 and TACCR2 CCIFG flags are set when the interrupt service routine

accesses the TAIV register, TACCR1 CCIFG is reset automatically. After the

RETI instruction of the interrupt service routine is executed, the TACCR2

CCIFG flag will generate another interrupt.