USART Registers: SPI Mode

14-15

USART Peripheral Interface, SPI Mode

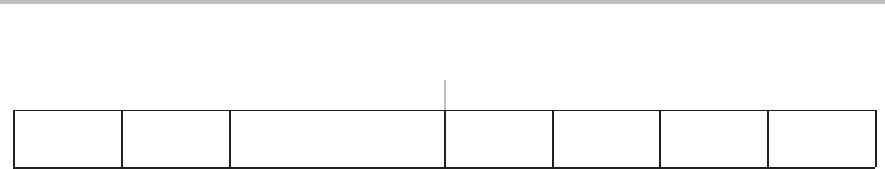

UxTCTL, USART Transmit Control Register

76543210

CKPH CKPL SSELx Unused Unused STC TXEPT

rw−0 rw−0 rw−0 rw−0 rw−0 rw−0 rw−0 rw−1

CKPH

Bit 7 Clock phase select. Controls the phase of UCLK.

0 Normal UCLK clocking scheme

1 UCLK is delayed by one half cycle

CKPL

Bit 6 Clock polarity select

0 The inactive level is low; data is output with the rising edge of UCLK;

input data is latched with the falling edge of UCLK.

1 The inactive level is high; data is output with the falling edge of

UCLK; input data is latched with the rising edge of UCLK.

SSELx

Bits

5-4

Source select. These bits select the BRCLK source clock.

00 External UCLK (valid for slave mode only)

01 ACLK (valid for master mode only)

10 SMCLK (valid for master mode only)

11 SMCLK (valid for master mode only)

Unused

Bit 3 Unused

Unused

Bit 2 Unused

STC

Bit 1 Slave transmit control.

0 4-pin SPI mode: STE enabled.

1 3-pin SPI mode: STE disabled.

TXEPT

Bit 0 Transmitter empty flag. The TXEPT flag is not used in slave mode.

0 Transmission active and/or data waiting in UxTXBUF

1 UxTXBUF and TX shift register are empty