ADC10 Operation

18-18

ADC10

Two-Block Transfer Mode

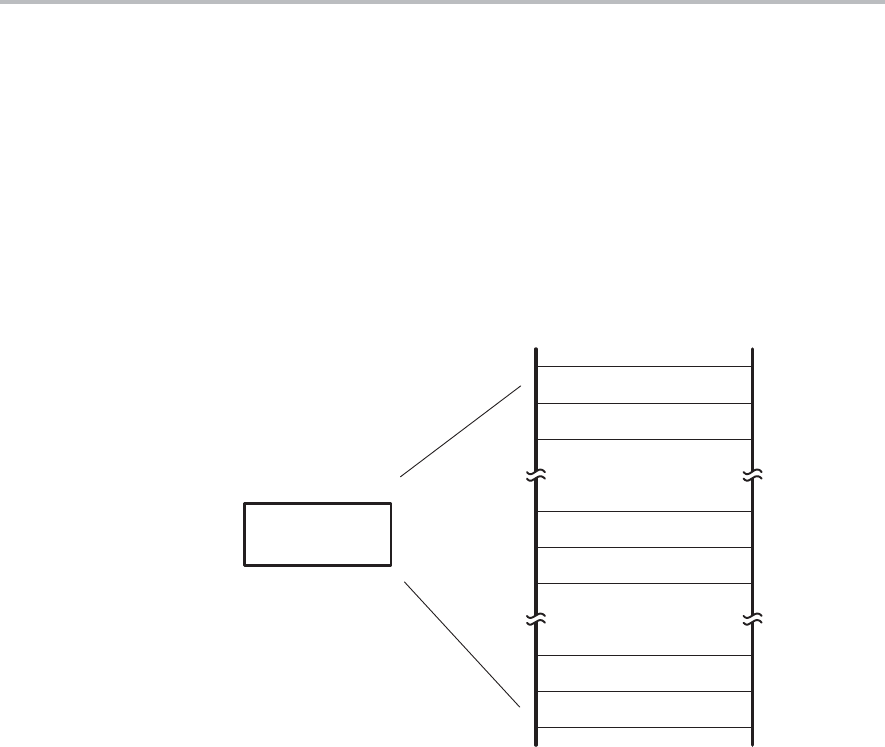

The two-block mode is selected if the ADC10TB bit is set. The value n in

ADC10DTC1 defines the number of transfers for one block. The address

range of the first block is defined anywhere in the MSP430 address range with

the 16-bit register ADC10SA. The first block ends at ADC10SA+2n–2. The

address range for the second block is defined as SA+2n to SA+4n–2. The

two-block transfer mode is shown in Figure 18−11.

Figure 18−11.Two-Block Transfer

ADC10SA

ADC10SA+2

ADC10SA+2n−2

ADC10SA+2n−4

1st transfer

’n’th transfer

2nd transfer

ADC10SA+4n−2

ADC10SA+4n−4

2 x ’n’th transfer

TB=1

DTC

The internal address pointer is initially equal to ADC10SA and the internal

transfer counter is initially equal to ‘n’. The internal pointer and counter are not

visible to software. The DTC transfers the word-value of ADC10MEM to the

address pointer ADC10SA. After each DTC transfer the internal address

pointer is incremented by two and the internal transfer counter is decremented

by one.

The DTC transfers continue, with each loading of ADC10MEM, until the

internal transfer counter becomes equal to zero. At this point, block one is full

and both the ADC10IFG flag the ADC10B1 bit are set. The user can test the

ADC10B1 bit to determine that block one is full.

The DTC continues with block two. The internal transfer counter is

automatically reloaded with ’n’. At the next load of the ADC10MEM, the DTC

begins transferring conversion results to block two. After n transfers have

completed, block two is full. The ADC10IFG flag is set and the ADC10B1 bit

is cleared. User software can test the cleared ADC10B1 bit to determine that

block two is full. Figure 18−12 shows a state diagram of the two-block mode.