Timer_B Operation

12-12

Timer_B

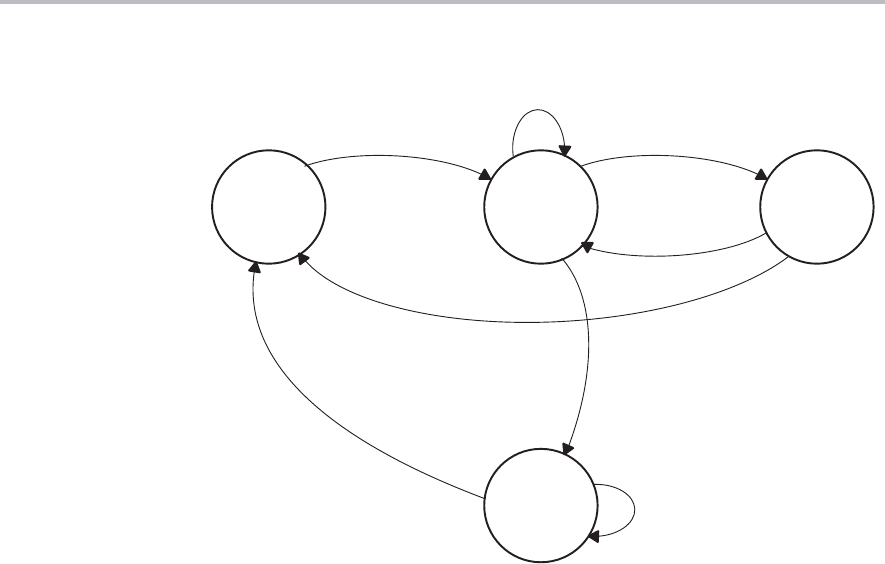

Figure 12−11.Capture Cycle

Second

Capture

Taken

COV = 1

Capture

Taken

No

Capture

Taken

Read

Taken

Capture

Clear Bit COV

in Register TBCCTLx

Idle

Idle

Capture

Capture Read and No Capture

Capture

Capture ReadCapture

Capture Initiated by Software

Captures can be initiated by software. The CMx bits can be set for capture on

both edges. Software then sets bit CCIS1=1 and toggles bit CCIS0 to switch

the capture signal between V

CC

and GND, initiating a capture each time

CCIS0 changes state:

MOV #CAP+SCS+CCIS1+CM_3,&TBCCTLx ; Setup TBCCTLx

XOR #CCIS0,&TBCCTLx ; TBCCTLx = TBR

Compare Mode

The compare mode is selected when CAP = 0. Compare mode is used to

generate PWM output signals or interrupts at specific time intervals. When

TBR counts to the value in a TBCLx:

- Interrupt flag CCIFG is set

- Internal signal EQUx = 1

- EQUx affects the output according to the output mode