Instruction Set

3-60

RISC 16−Bit CPU

RRA[.W] Rotate right arithmetically

RRA.B Rotate right arithmetically

Syntax RRA dst or RRA.W dst

RRA.B dst

Operation MSB −> MSB, MSB −> MSB−1, ... LSB+1 −> LSB, LSB −> C

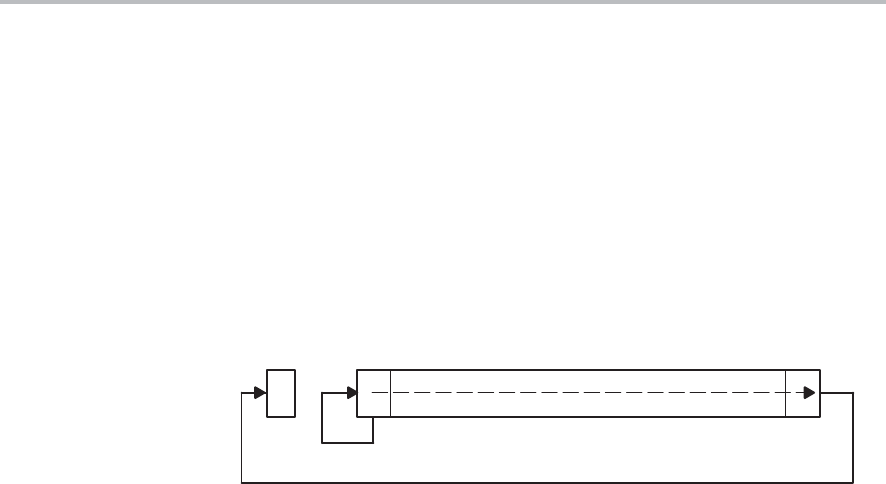

Description The destination operand is shifted right one position as shown in Figure 3−16.

The MSB is shifted into the MSB, the MSB is shifted into the MSB−1, and the

LSB+1 is shifted into the LSB.

Figure 3−16. Destination Operand—Arithmetic Right Shift

15 0

15

0

C

Byte

Word

Status Bits N: Set if result is negative, reset if positive

Z: Set if result is zero, reset otherwise

C: Loaded from the LSB

V: Reset

Mode Bits OSCOFF, CPUOFF, and GIE are not affected.

Example R5 is shifted right one position. The MSB retains the old value. It operates

equal to an arithmetic division by 2.

RRA R5 ; R5/2 −> R5

; The value in R5 is multiplied by 0.75 (0.5 + 0.25).

;

PUSH R5 ; Hold R5 temporarily using stack

RRA R5 ; R5 × 0.5 −> R5

ADD @SP+,R5 ; R5 × 0.5 + R5 = 1.5 × R5 −> R5

RRA R5 ; (1.5 × R5) × 0.5 = 0.75 × R5 −> R5

......

Example The low byte of R5 is shifted right one position. The MSB retains the old value.

It operates equal to an arithmetic division by 2.

RRA.B R5 ; R5/2 −> R5: operation is on low byte only

; High byte of R5 is reset

PUSH.B R5 ; R5 × 0.5 −> TOS

RRA.B @SP ; TOS × 0.5 = 0.5 × R5 × 0.5 = 0.25 × R5 −> TOS

ADD.B @SP+,R5 ; R5 × 0.5 + R5 × 0.25 = 0.75 × R5 −> R5

......