System Reset and Initialization

2-10

System Resets, Interrupts, and Operating Modes

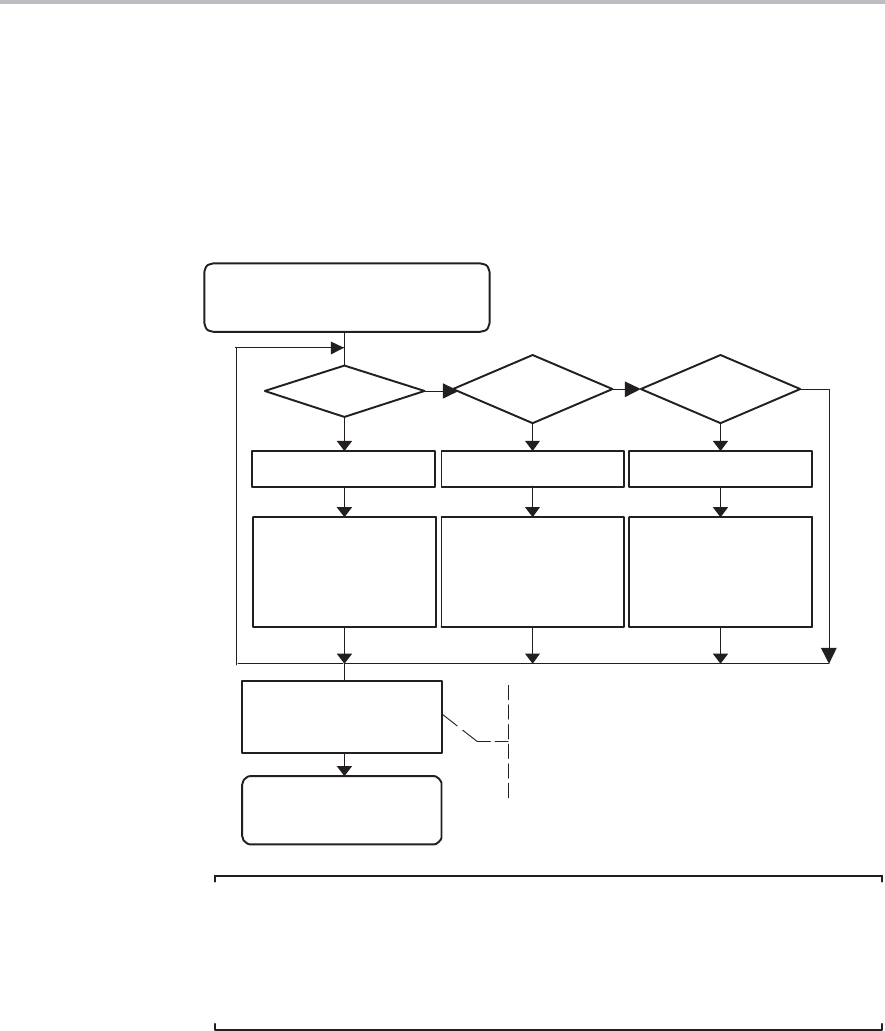

Example of an NMI Interrupt Handler

The NMI interrupt is a multiple-source interrupt. An NMI interrupt automatically

resets the NMIIE, OFIE and ACCVIE interrupt-enable bits. The user NMI

service routine resets the interrupt flags and re-enables the interrupt-enable

bits according to the application needs as shown in Figure 2−6.

Figure 2−6. NMI Interrupt Handler

yes

no

OFIFG=1

yes

no

ACCVIFG=1

yes

Reset ACCVIFG

no

NMIIFG=1

Reset NMIIFGReset OFIFG

Start of NMI Interrupt Handler

Reset by HW:

OFIE, NMIIE, ACCVIE

User’s Software,

Oscillator Fault

Handler

User’s Software,

Flash Access

Violation Handler

User’s Software,

External NMI

Handler

Optional

Set NMIIE, OFIE,

ACCVIE Within One

Instruction

RETI

End of NMI Interrupt

Handler

Example 1:

Example 2:

BIS #(NMIIE+OFIE+ACCVIE), &IE1

BIS Mask,&IE1 ; Mask enables only

; interrupt sources

Note: Enabling NMI Interrupts with ACCVIE, NMIIE, and OFIE

The ACCVIE, NMIIE, and OFIE enable bits should not be set inside of an NMI

interrupt service routine, unless they are set by the last instruction of the

routine before the RETI instruction. Otherwise, nested NMI interrupts may

occur, causing stack overflow and unpredictable operation.

2.2.2 Maskable Interrupts

Maskable interrupts are caused by peripherals with interrupt capability

including the watchdog timer overflow in interval-timer mode. Each maskable

interrupt source can be disabled individually by an interrupt enable bit, or all

maskable interrupts can be disabled by the general interrupt enable (GIE) bit

in the status register (SR).