Addressing Modes

3-10

RISC 16-Bit CPU

3.3.1 Register Mode

The register mode is described in Table 3−4.

Table 3−4.Register Mode Description

Assembler Code Content of ROM

MOV R10,R11 MOV R10,R11

Length: One or two words

Operation: Move the content of R10 to R11. R10 is not affected.

Comment: Valid for source and destination

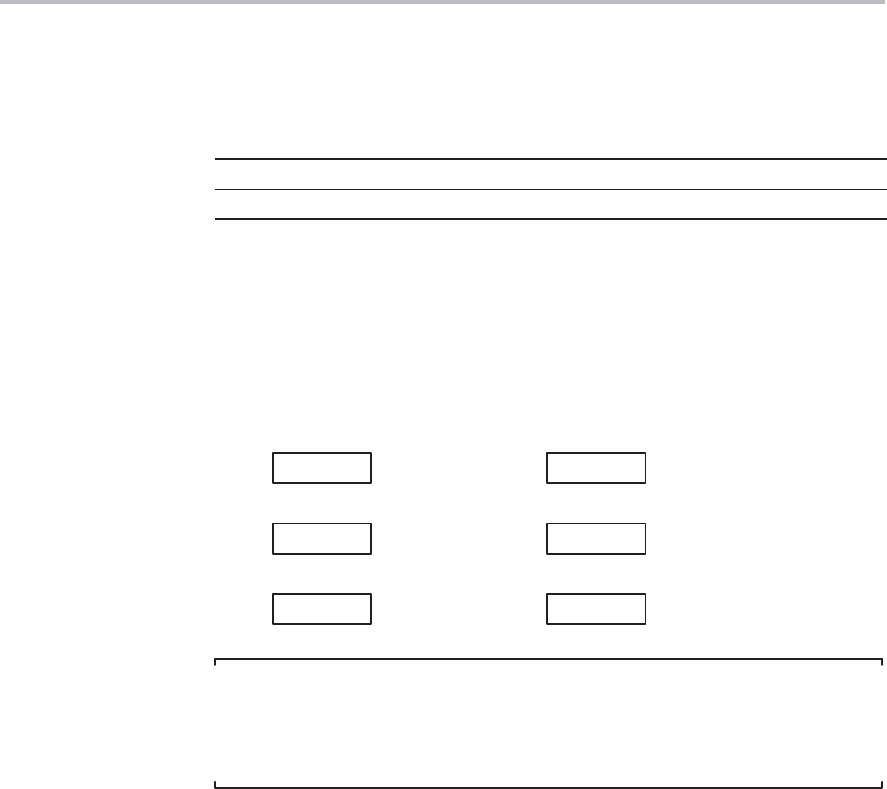

Example: MOV R10,R11

0A023hR10

R11

Before: After:

PC

0FA15h

PC

old

0A023hR10

R11

PC PC

old

+ 2

0A023h

Note: Data in Registers

The data in the register can be accessed using word or byte instructions. If

byte instructions are used, the high byte is always 0 in the result. The status

bits are handled according to the result of the byte instruction.