Instruction Set

3-61

RISC 16−Bit CPU

RRC[.W] Rotate right through carry

RRC.B Rotate right through carry

Syntax RRC dst or RRC.W dst

RRC dst

Operation C −> MSB −> MSB−1 .... LSB+1 −> LSB −> C

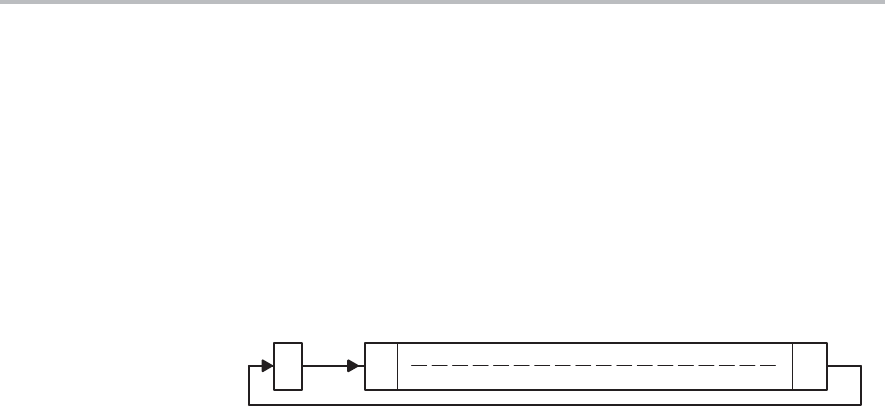

Description The destination operand is shifted right one position as shown in Figure 3−17.

The carry bit (C) is shifted into the MSB, the LSB is shifted into the carry bit (C).

Figure 3−17. Destination Operand—Carry Right Shift

15 0

70

C

Byte

Word

Status Bits N: Set if result is negative, reset if positive

Z: Set if result is zero, reset otherwise

C: Loaded from the LSB

V: Set if initial destination is positive and initial carry is set, otherwise reset

Mode Bits OSCOFF, CPUOFF, and GIE are not affected.

Example R5 is shifted right one position. The MSB is loaded with 1.

SETC ; Prepare carry for MSB

RRC R5 ; R5/2 + 8000h −> R5

Example R5 is shifted right one position. The MSB is loaded with 1.

SETC ; Prepare carry for MSB

RRC.B R5 ; R5/2 + 80h −> R5; low byte of R5 is used