Comparator_A Operation

16-6

Comparator_A

16.2.5 Comparator_A, Port Disable Register CAPD

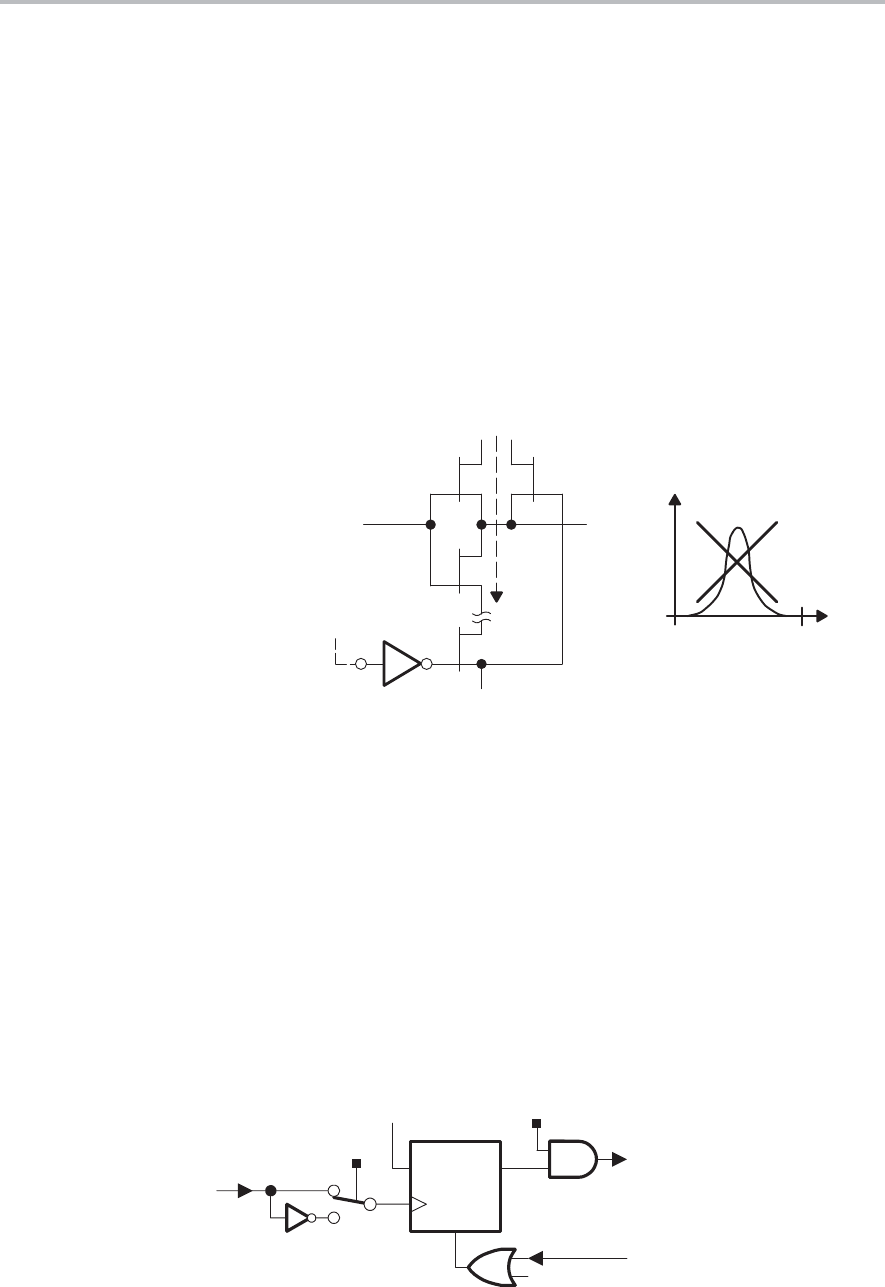

The comparator input and output functions are multiplexed with the associated

I/O port pins, which are digital CMOS gates. When analog signals are applied

to digital CMOS gates, parasitic current can flow from V

CC

to GND. This

parasitic current occurs if the input voltage is near the transition level of the

gate. Disabling the port pin buffer eliminates the parasitic current flow and

therefore reduces overall current consumption.

The CAPDx bits, when set, disable the corresponding P2 input buffer as shown

in Figure 16−3. When current consumption is critical, any P2 pin connected to

analog signals should be disabled with their associated CAPDx bit.

Figure 16−3. Transfer Characteristic and Power Dissipation in a CMOS Inverter/Buffer

V

CC

V

SS

I

CC

V

O

VI

0V

CC

VI

V

CC

I

CC

CAPD.x = 1

16.2.6 Comparator_A Interrupts

One interrupt flag and one interrupt vector are associated with the

Comparator_A as shown in Figure 16−4. The interrupt flag CAIFG is set on

either the rising or falling edge of the comparator output, selected by the

CAIES bit. If both the CAIE and the GIE bits are set, then the CAIFG flag

generates an interrupt request. The CAIFG flag is automatically reset when

the interrupt request is serviced or may be reset with software.

Figure 16−4. Comparator_A Interrupt System

DQ

IRQ, Interrupt Service Requested

Reset

V

CC

POR

SET_CAIFG

IRACC, Interrupt Request Accepted

CAIE

CAIES

0

1