I

2

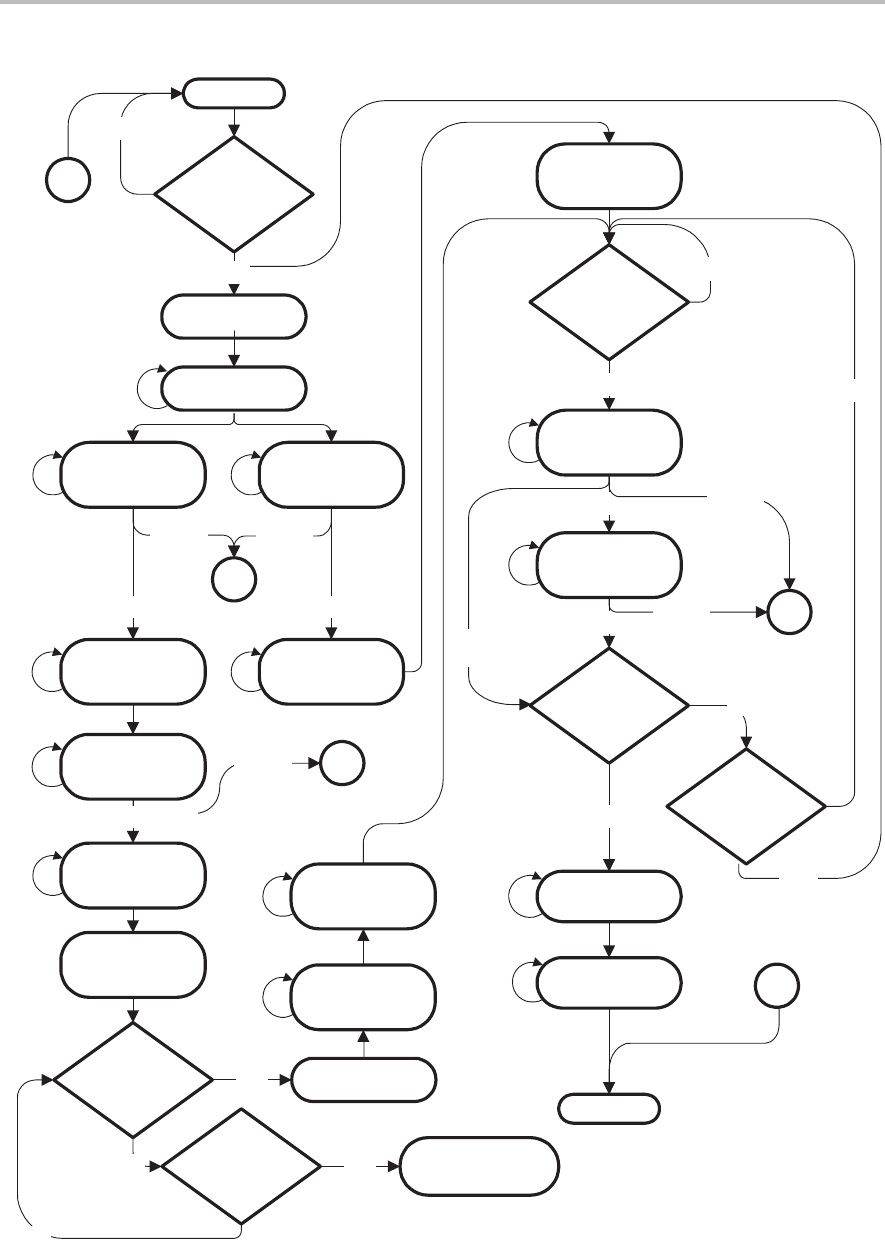

C Module Operation

15-13

USART Peripheral Interface, I

2

C Mode

Figure 15−11.Slave Transmitter

I2CBB Is Cleared

Send Data

Low Byte

To Master

2nd Start

Detected?

Send Data

High Byte

To Master

Ack

Ack

8 x SCL

8 x SCL

STTIFG Is Set

I2CBUSY Is Set

START

Detected?

I2CBB Is Set

Send

Acknowledge

1 x SCL

4 x I2CPSC

8 x SCL

IDLE

Receive Slave

Address Bits 9−8

with R/W = 0

OAIFG Set If Not

RESTART

8 x SCL

No

STOP Detected?

STTIFG Is Set

No

Receive Slave

Address Bits 9−8

with R/W=1

8 x SCL

Send

Acknowledge

1 x SCL

OAIFG Set If Not

RESTART

I2CDR Loaded?

I2CBUSY Is

Cleared

1

RESTART

Detected?

1

Yes

Yes

No Ack

No Ack

No

No

I2CDR Empty

Yes

Yes

Ack and

I2CWORD=0

4 x I2CPSC

13 x I2CPSC

IDLE

Receive Slave

Address Bits 7−0

8 x SCL

Send

Acknowledge

1 x SCL

Send

Acknowledge

1 x SCL

XA = 0

Yes

2

Matched I2COA Matched I2COA

No

Match

No

Match

XA = 1

2

2

No

Match

Matched I2COA

Data

on SDA?

No

Yes

Enter Slave Receive

mode at ”1”

Receive Slave

Address Bits 6−0

with R/W = 1