ADC10 Operation

18-23

ADC10

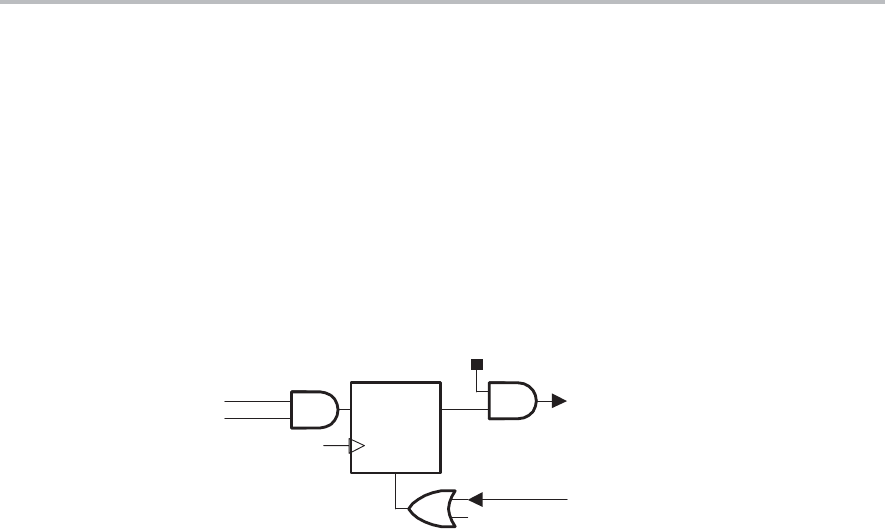

18.2.10 ADC10 Interrupts

One interrupt and one interrupt vector are associated with the ADC10 as

shown in Figure 18−17. When the DTC is not used (ADC10DTC1 = 0)

ADC10IFG is set when conversion results are loaded into ADC10MEM. When

DTC is used (ADC10DTC1 > 0) ADC10IFG is set when a block transfer

completes and the internal transfer counter ’n’ = 0. If both the ADC10IE and

the GIE bits are set, then the ADC10IFG flag generates an interrupt request.

The ADC10IFG flag is automatically reset when the interrupt request is

serviced or may be reset by software.

Figure 18−17. ADC10 Interrupt System

DQ

IRQ, Interrupt Service Requested

Reset

ADC10CLK

POR

’n’ = 0

Set ADC10IFG

IRACC, Interrupt Request Accepted

ADC10IE