USART Registers: SPI Mode

14-13

USART Peripheral Interface, SPI Mode

14.3 USART Registers: SPI Mode

The USART registers, shown in Table 14−1 and Table 14−2, are byte

structured and should be accessed using byte instructions.

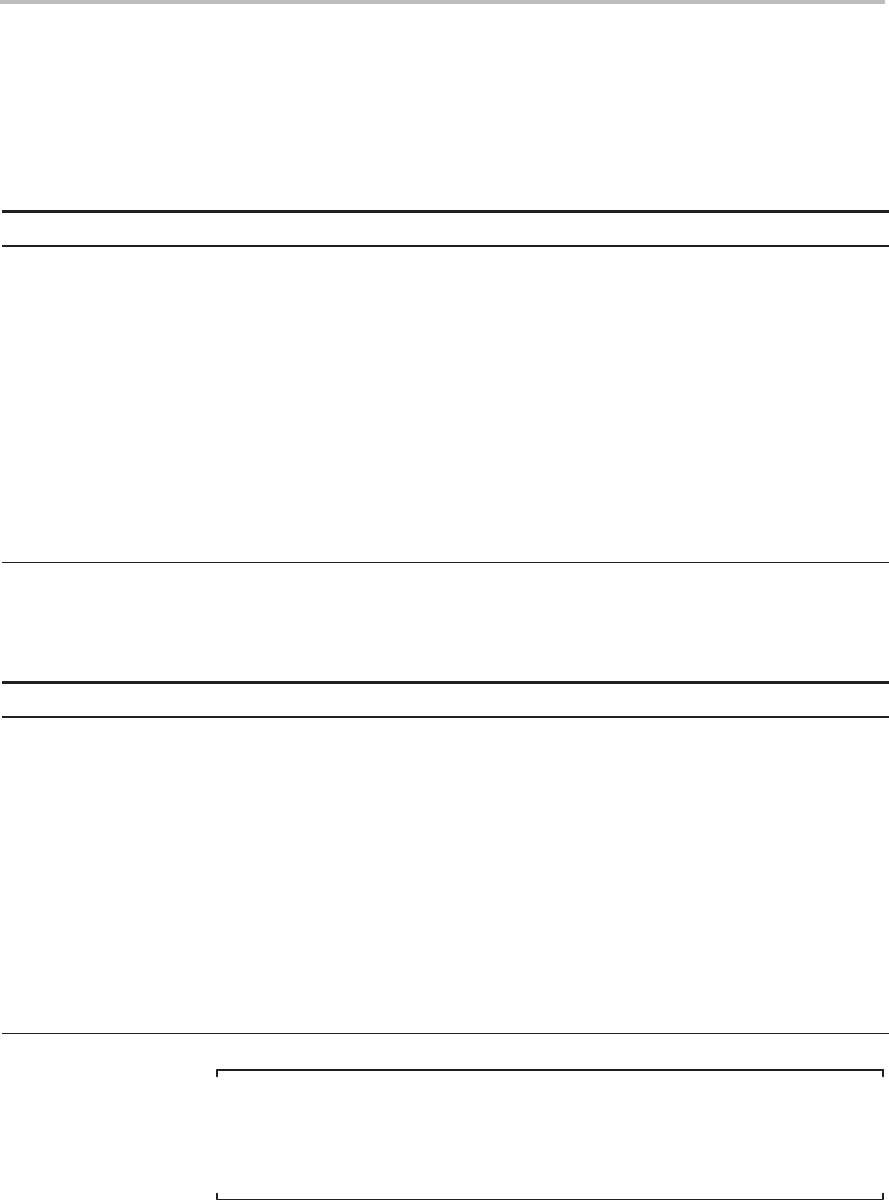

Table 14−1.USART0 Control and Status Registers

Register Short Form Register Type Address Initial State

USART control register U0CTL Read/write 070h 001h with PUC

Transmit control register U0TCTL Read/write 071h 001h with PUC

Receive control register U0RCTL Read/write 072h 000h with PUC

Modulation control register U0MCTL Read/write 073h Unchanged

Baud rate control register 0 U0BR0 Read/write 074h Unchanged

Baud rate control register 1 U0BR1 Read/write 075h Unchanged

Receive buffer register U0RXBUF Read 076h Unchanged

Transmit buffer register U0TXBUF Read/write 077h Unchanged

SFR module enable register 1

†

ME1 Read/write 004h 000h with PUC

SFR interrupt enable register 1

†

IE1 Read/write 000h 000h with PUC

SFR interrupt flag register 1

†

IFG1 Read/write 002h 082h with PUC

†

Does not apply to MSP430x12xx devices. Refer to the register definitions for registers and bit positions for these devices.

Table 14−2.USART1 Control and Status Registers

Register Short Form Register Type Address Initial State

USART control register U1CTL Read/write 078h 001h with PUC

Transmit control register U1TCTL Read/write 079h 001h with PUC

Receive control register U1RCTL Read/write 07Ah 000h with PUC

Modulation control register U1MCTL Read/write 07Bh Unchanged

Baud rate control register 0 U1BR0 Read/write 07Ch Unchanged

Baud rate control register 1 U1BR1 Read/write 07Dh Unchanged

Receive buffer register U1RXBUF Read 07Eh Unchanged

Transmit buffer register U1TXBUF Read/write 07Fh Unchanged

SFR module enable register 2 ME2 Read/write 005h 000h with PUC

SFR interrupt enable register 2 IE2 Read/write 001h 000h with PUC

SFR interrupt flag register 2

IFG2 Read/write 003h 020h with PUC

Note: Modifying the SFR bits

To avoid modifying control bits for other modules, it is recommended to set

or clear the IEx and IFGx bits using BIS.B or BIC.B instructions, rather than

MOV.B or CLR.B instructions.