TMP92CM22

2007-02-16

92CM22-119

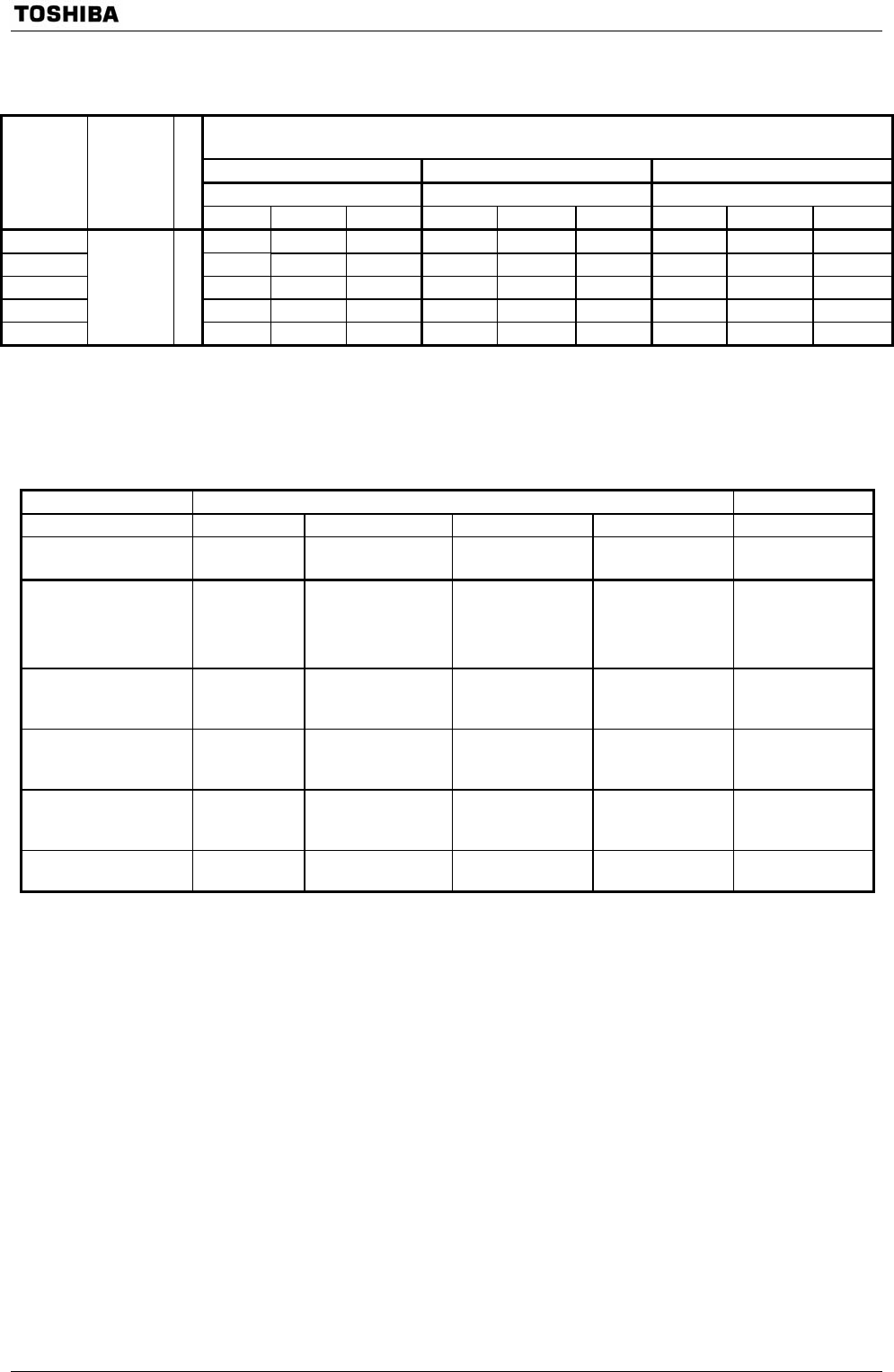

Table 3.7.4 Relationship of PWM Cycle and 2

n

Counter

PWM cycle

TAxxMOD<PWMx1:0>

2

6

(x64) 2

7

(x128) 2

8

(x256)

TAxxMOD<TAxCLK1:0> TAxxMOD<TAxCLK1:0> TAxxMOD<TAxCLK1:0>

Clock gear

SYSCR1

<GEAR2:0>

System clock

SYSCR0

<SYSCK>

−

φT1(x2) φT4(x8) φT16(x32) φT1(x2) φT4(x8) φT16(x32) φT1(x2) φT4(x8) φT16(x32)

000(x1) 1024/fc 4096/fc 16384/fc 2048/fc 8192/fc 32768/fc 4096/fc 16384/fc 65536/fc

001(x2) 2048/fc 8192/fc 32768/fc 4096/fc 16384/fc 65536/fc 8192/fc 32768/fc 131072/fc

010(x4) 4096/fc 16384/fc 65536/fc 8192/fc 32768/fc 131072/fc 16384/fc 65536/fc 262144/fc

011(x8) 8192/fc 32768/fc 131072/fc 16384/fc 65536/fc 262144/fc 32768/fc 131072/fc 524288/fc

100(x16)

0(fc) ×8

16384/fc 65536/fc 262144/fc 32768/fc 131072/fc 524288/fc 65536/fc 262144/fc 1048576/fc

(5) Mode settings

Table 3.7.5 shows the SFR settings for each mode.

Table 3.7.5 Timer Mode Setting Registers

Register Name TA01MOD TA1FFCR

<Bit symbol> <TA01M1:0> <PWM01:00> <TA1CLK1:0> <TA0CLK1:0> <TA1FFIS>

Function Timer mode PWM cycle

Upper timer

input clock

Lower timer

input clock

Timer F/F

inversion select

8-bit timer × 2 channels 00 −

Lower timer match,

φT1, φT16, φT256

(00, 01, 10, 11)

External

φT1, φT4, φT16

(00, 01, 10, 11)

0: Lower timer

output

1: Upper timer

output

16-bit timer mode 01 − −

External

φT1, φT4, φT16

(00, 01, 10, 11)

−

8-bit PPG × 1 channel 10 − −

External

φT1, φT4, φT16

(00, 01, 10, 11)

−

8-bit PWM × 1 channel 11

2

6

, 2

7

, 2

8

(01, 10, 11)

−

External

φT1, φT4, φT16

(00, 01, 10, 11)

−

8-bit timer × 1 channel 11 −

φT1, φT16, φT256

(01, 10, 11)

− Output disable

− : Don’t care