TMP92CM22

2007-02-16

92CM22-39

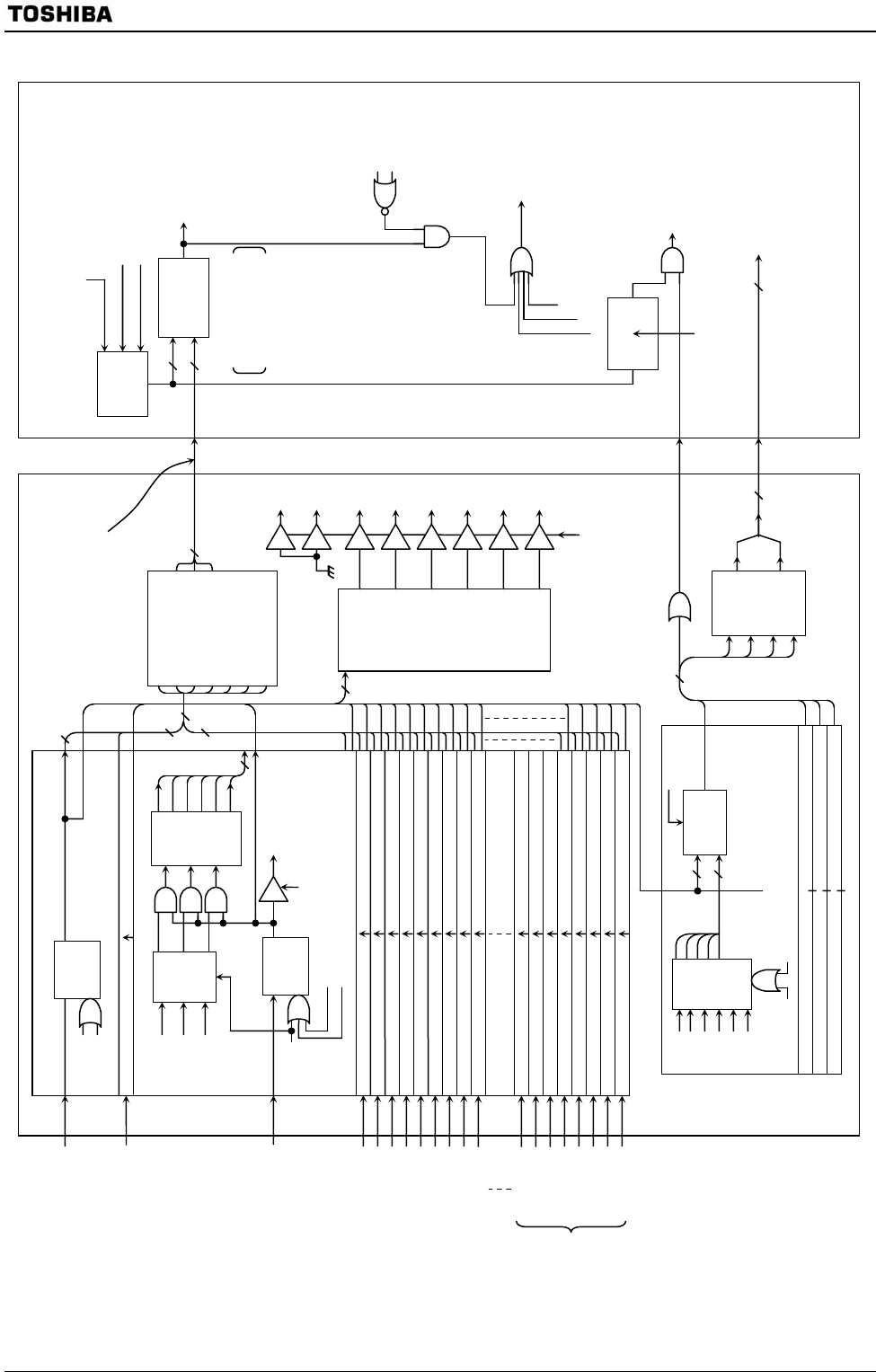

Figure 3.4.3 Block Diagram of Interrupt Controller

Interrupt request

signal to CPU

Micro DMA start vector setting register

During STOP

36

3

3

3

1

6

2

2

4

6

34

4-input OR

INT0 to INT3

Micro DMA channel

p

riorit

y

encode

r

Priority encode

r

DMA0V

DMA1V

DMA2V

DMA3V

Reset

Interrupt request flag

Reset

Reset

Priorit

y

settin

g

re

g

iste

r

V = 20H

V = 24H

Interrupt controlle

r

CPU

S Q

R

V = 28H

V = 2CH

V = 30H

V = 34H

V = 38H

V = 3CH

V = 40H

V = 44H

V = 48H

V = 4CH

V = D0H

V = D4H

V = D8H

V = DCH

V = E0H

V = E4H

V = E8H

V = ECH

D Q

CLR

A

B

C

Dn

Dn + 1

Dn + 2

Interrupt

request flag

Interrupt vector read

Micro DMA acknowlege

Interrupt request F/F read

Dn + 3

A

B

C

I

n

t

errup

t

vector read

D2

D3

D4

D5

D6

D7

0

1

2

3

A

B

D0

D1

Interrupt enable

flag in CPU side

Micro DMA request

Release halt

INTRQ2 to 0 ≥ IFF

2 to 0 then1

INTRQ2 to 0

IFF2:0

Reset

EI1 to 7

DI

Interrupt request

signal

Micro DMA

channel

specification

RESET

INTWD

INT0

INT1

INT2

INT3

(Reserved)

(Reserved)

(Reserved)

(Reserved)

(Reserved)

(Reserved)

INTTC0

INTTC1

INTTC2

INTTC3

INTTC4

INTTC5

INTTC6

INTTC7

Interrupt

vector

generator

Highest

priority interrupt

level select

1

2

3

4

5

6

7

D5

D4

D3

D2

D1

D0

Decode

r

Y1

Y2

Y3

Y4

Y5

Y6

S Q

R

7

1

6

(Highest priority

is “7”.)

Interuupt

level detect

D Q

CLR

S

Selector

Interrupt vector V

read

INTTC0

Soft start

Micro DMA

counte

r

0

interrupt

If IFF = 7 then 0

NMI

(Reserved)

During IDLE1