TMP92CM22

2007-02-16

92CM22-220

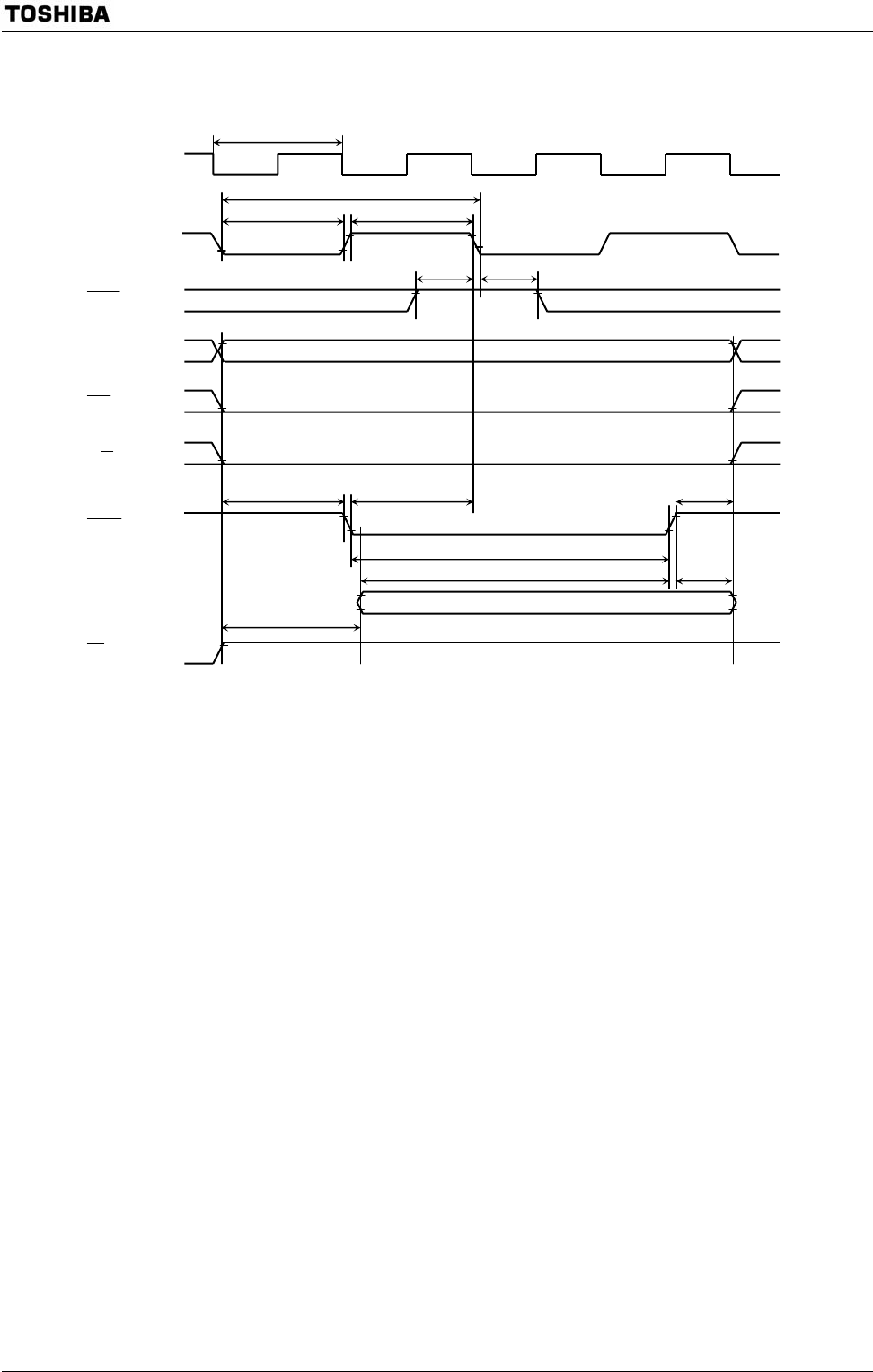

(2) Write cycle (0 waits, fc = f

OSCH

, f

FPH

= fc/1)

Note: The phase relation between X1 input signal and the other signals is unsettled.

The timing chart above is an example.

X1

CLKOUT

A

0 to A23

D0 to D31

WAIT

RD

Data output

t

OSC

t

CL

t

CH

t

CYC

t

TK

t

KT

t

AW

t

WK

t

WA

t

WW

t

DW

t

WD

t

RDO

CSx

WRxx

R/

W