TMP92CM22

2007-02-16

92CM22-242

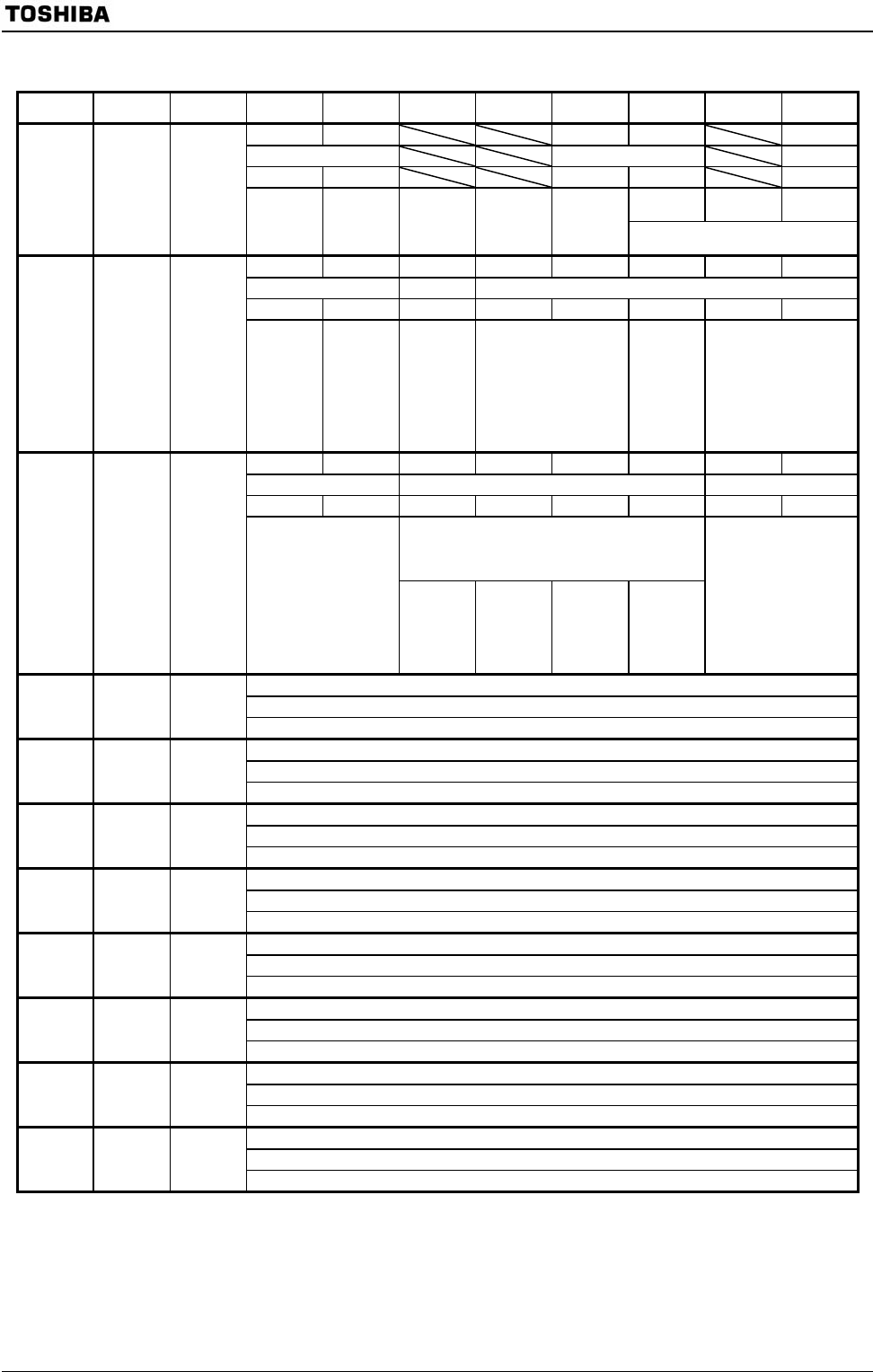

(7) 16-bit timer (1/2)

Symbol Name

Address 7 6 5 4 3 2 1 0

TB0RDE − I2TB0 TB0PRUN TB0RUN

R/W R/W R/W

0 0 0 0 0

TMRB0

prescaler

UP counter

(UC10)

TB0RUN

Timer B0

RUN

register

1180H

Double

buffer

0: Disable

1: Enable

Always

write “0”.

IDLE2

0: Stop

1: Operate

0: Stop and clear

1: Run (Count up)

− − TB0CP0I TB0CPM1 TB0CPM0 TB0CLE TB0CLK1 TB0CLK0

R/W W R/W

0 0 1 0 0 0 0 0

TB0MOD

Timer B0

mode

register

1182H

(Prohibit

RMW)

Always

write “0”.

Always

write “0”.

Software

capture

control

0: Software

capture

1: Undefined

Capture timing

00: Disable

01: Reserved

10: Reserved

11: TA1OUT↑

TA1OUT↓

Up counter

control

0: Clear

disable

1: Clear

enable

Timer B0 source clock

00: Reserved

01: φT1

10: φT4

11: φT16

− − TB0C1T1 TB0C0T1 TB0E1T1 TB0E0T1 TB0FFC1 TB0FFC0

W* R/W W*

1 1 0 0 0 0 1 1

TB0FF0 inversion trigger

0: Trigger disable

1: Trigger enable

TB0FFCR

Timer B0

flip-flop

control

register

1183H

(Prohibit

RMW)

Always write “11”.

Invert when

the UC10

value is

loaded in to

TB0CP1H/L.

Invert when

the UC10

value is

loaded in to

TB0CP0H/L.

Invert when

the UC10

matches with

TB0RG1H/L.

Invert when

the UC10

matches with

TB0RG0H/L.

Control TB0FF0

00: Invert

01: Set

10: Clear

11: Don’t care

* Always read as 11.

−

W

TB0RG0L

16-bit timer

register 0

low

1188H

(Prohibit

RMW)

Undefined

−

W

TB0RG0H

16-bit timer

register 0

high

1189H

(Prohibit

RMW)

Undefined

−

W

TB0RG1L

16-bit timer

register 1

low

118AH

(Prohibit

RMW)

Undefined

−

W

TB0RG1H

16-bit timer

register 1

high

118BH

(Prohibit

RMW)

Undefined

−

R

TB0CP0L

Capture

register 0

low

118CH

Undefined

−

R

TB0CP0H

Capture

register 0

high

118DH

Undefined

−

R

TB0CP1L

Capture

register 1

low

118EH

Undefined

−

R

TB0CP1H

Capture

register 1

high

118FH

Undefined