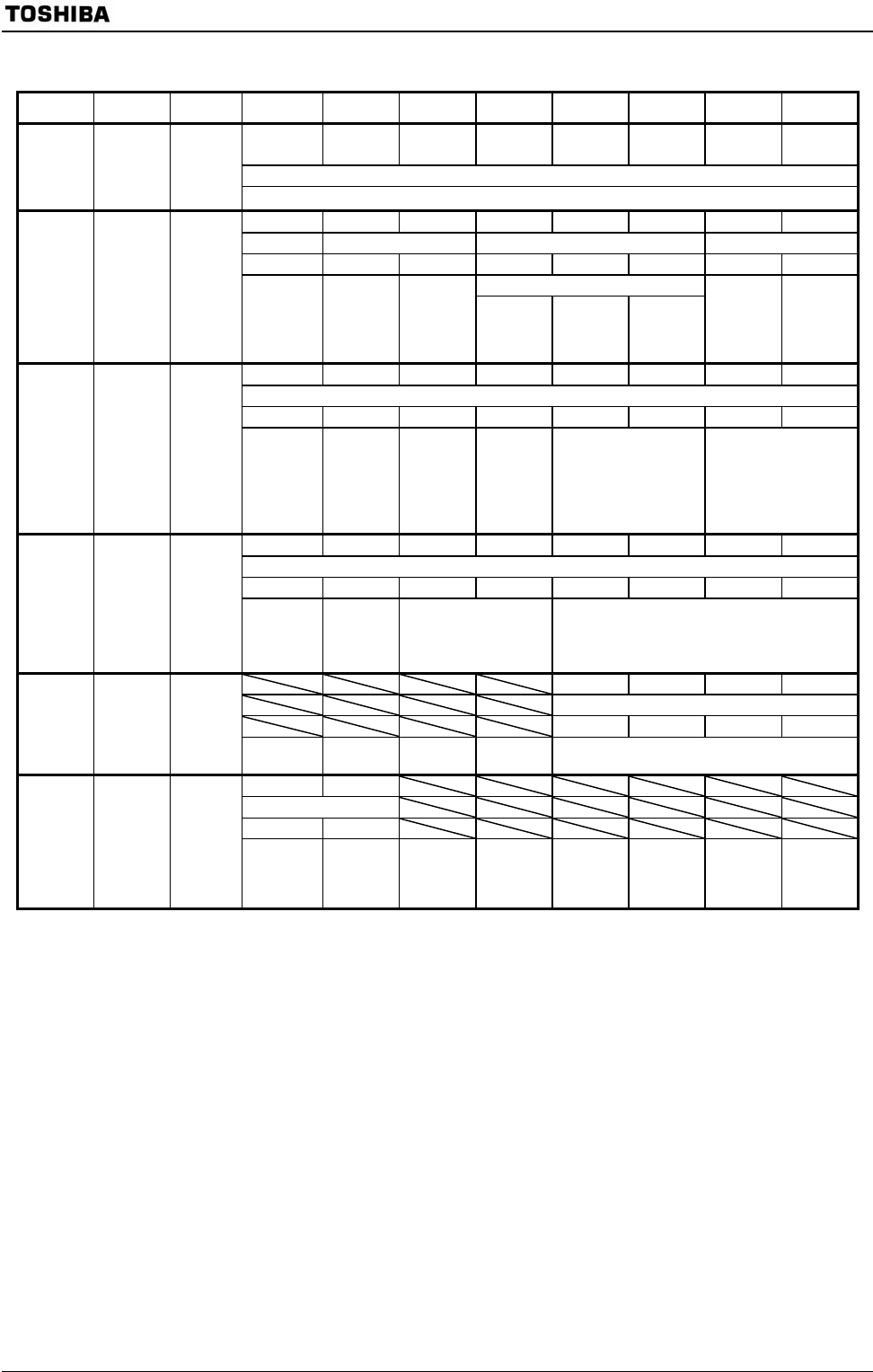

TMP92CM22

2007-02-16

92CM22-245

UART/Serial channel (2/2)

Symbol Name

Address 7 6 5 4 3 2 1 0

RB7

TB7

RB6

TB6

RB5

TB5

RB4

TB4

RB3

TB3

RB2

TB2

RB1

TB1

RB0

TB0

R (Receiving)/W (Transmission)

SC1BUF

Serial

channel 1

buffer

register

1208H

(Prohibit

RMW)

Undefined

RB8 EVEN PE OERR PERR FERR SCLKS IOC

R R/W R (Clear 0 after reading) R/W

Undefined 0 0 0 0 0 0 0

1: Error

SC1CR

Serial

channel 1

control

register

1209H

Receive

data

bit8

Parity

0: Odd

1: Even

Parity

0: Disable

1: Enable

Overrun

Parity Framing

0: SCLK1↑

1: SCLK1↓

0:Baud

rate

generator

1:SCLK1

pin input

TB8 CTSE RXE WU SM1 SM0 SC1 SC0

R/W

0 0 0 0 0 0 0 0

SC1MOD0

Serial

channel 1

mode 0

register

120AH

Transmis-

sion data

bit8

0: CTS

disable

1: CTS

enable

0: Receive

disable

1: Receive

enable

Wake up

0: Disable

1: Enable

00: I/O interface mode

01: 7-bit UART mode

10: 8-bit UART mode

11: 9-bit UART mode

00: Timer TA0REG

01: Baud rate

generator

10: Internal clock f

IO

11: External clock

(SCLK1 input)

− BR1ADDE BR1CK1 BR1CK0 BR1S3 BR1S2 BR1S1 BR1S0

R/W

0 0 0 0 0 0 0 0

BR1CR

Serial

channel 1

baud rate

control

register

120BH

Always

write “0”.

(16 − K)/

16 divided

0: Disable

1: Enable

00: φT0

01: φT2

10: φT8

11: φT32

Divided frequency setting

BR1K3 BR1K2 BR1K1 BR1K0

R/W

0 0 0 0

BR1ADD

Serial

channel 1

K setting

register

120CH

Sets frequency divisor “K”

(divided by N + (16 − K)/16).

I2S1 FDPX1

R/W

0 0

SC1MOD1

Serial

channel 1

mode 1

register

120DH

IDLE2

0: Stop

1: Operate

I/O interface

mode

0: Half duplex

1: Full duplex