TMP92CM22

2007-02-16

92CM22-162

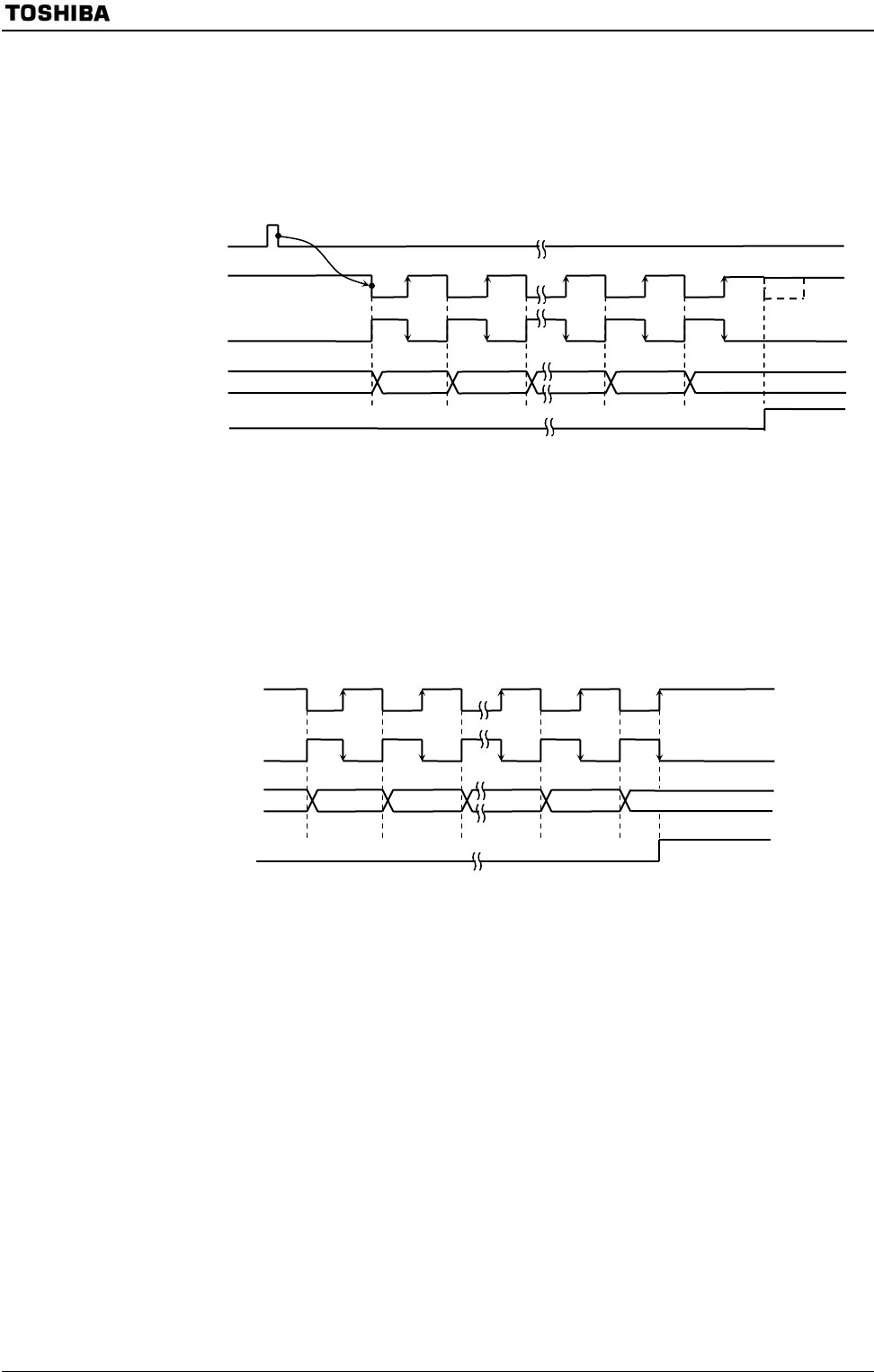

Bit0 Bit1 Bit6 Bit5

SCLK0 input

(<SCLKS> = 0

rising mode)

SCLK0 input

(<SCLKS> = 1

falling mode)

TXD0

ITX0C

(INTTX0 interrupt

request)

1. Transmission

In SCLK output mode 8-bit data and a synchronous clock are output on the

TXD0 and SCLK0 pins respectively each time the CPU writes the data to the

transmission buffer. When all data is outputted, INTES0<ITX0C> will be set to

generate the INTTX0 interrupt.

Figure 3.9.19 Transmission Operation in I/O Interface Mode (SCLK0 output mode)

In SCLK input mode, 8-bit data is output from the TXD0 pin when the SCLK0

input becomes active after the data has been written to the transmission buffer by

the CPU.

When all data is outputted, INTES0<ITX0C> will be set to generate INTTX0

interrupt.

Figure 3.9.20 Transmission Operation in I/O Interface Mode (SCLK0 input mode)

Bit7

SCLK0 output

(<SCLKS> = 0

rising mode)

Bit7

Bit0 Bit1 Bit6

Timing of writing

transmission data

TXD0

ITX0C

(INTTX0 interrupt

request)

SCLK0 output

(<SCLKS> = 1

falling mode)

(Internal clock

timinig)