TMP92CM22

2007-02-16

92CM22-145

3.9.2 Operation of Each Circuit

(1) Prescaler

There is a 6-bit prescaler for generating a clock to SIO0. The clock selected using

SYSCR1<GEAR2:0> is divided by 8 and input to the prescaler as φT0. The prescaler

can be run only case of selecting the baud rate generator as the serial transfer clock.

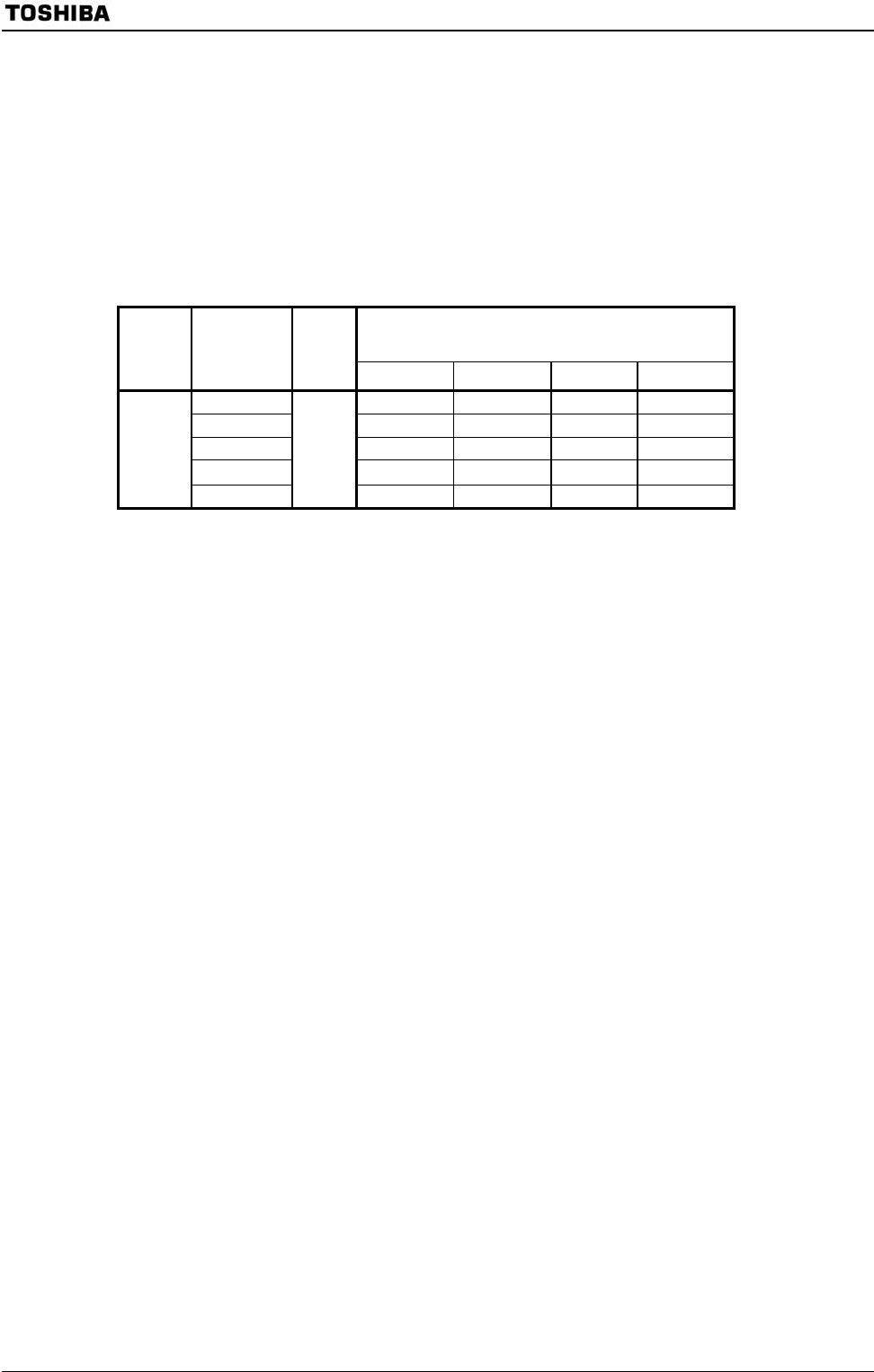

Table 3.9.2 shows prescaler clock resolution into the baud rate generator.

Table 3.9.2 Prescaler Clock Resolution to Baud Rate Generator

Clock Resolution

BR0CR<BR0CK1:0>

−

Clock Gear

SYSCR1

<GEAR2:0>

−

φT0 φT2 φT8 φT32

000(1/1) fc/8 fc/32 fc/128 fc/512

001(1/2) fc/16

fc/64 fc/256 fc/1024

010(1/4) fc/32

fc/128 fc/512 fc/2048

011(1/8)

fc/64

fc/256 fc/1024 fc/4096

fc

100(1/16)

1/8

fc/128 fc/512 fc/2048 fc/8192

The serial interface baud rate generator selects between 4 clock inputs: φT0, φT2,

φT8, and φT32 among the prescaler outputs.