TMP92CM22

2007-02-16

92CM22-180

(6) Transmitter/receiver selection

Set the SBI0CR2<TRX> to “1” for operating the TMP92CM22 as a transmitter. Clear

the <TRX> to “0” for operation as a receiver. In slave mode, when transfer data in

addressing format, when received slave address is same value with setting value to

I2C0AR, or GENERAL CALL is received (All 8-bit data are “0” after a start condition),

the <TRX> is set to “1” by the hardware if the direction bit (R/

W ) sent from the master

device is “1”, and <TRX> is cleared to “0” by the hardware if the bit is “0”.

In the master mode, after an acknowledge signal is returned from the slave device,

the <TRX> is cleared to “0” by the hardware if a transmitted direction bit is “1”, and is

set to “1” by the hardware if it is “0”. When an acknowledge signal is not returned, the

current condition is maintained.

The <TRX> is cleared to “0” by the hardware after a stop condition on the bus is

detected or arbitration is lost.

(7) Start/stop condition generation

When programmed “1111” to SBI0CR2 <MST, TRX, BB, PIN> in during

SBI0SR<BB> is “0”, slave address and direction bit which are set to SBI0DBR and

start condition are output on a bus. And it is necessary to set transmitted data to the

data buffer register (SBI0DBR) and set “1” to <ACK> beforehand.

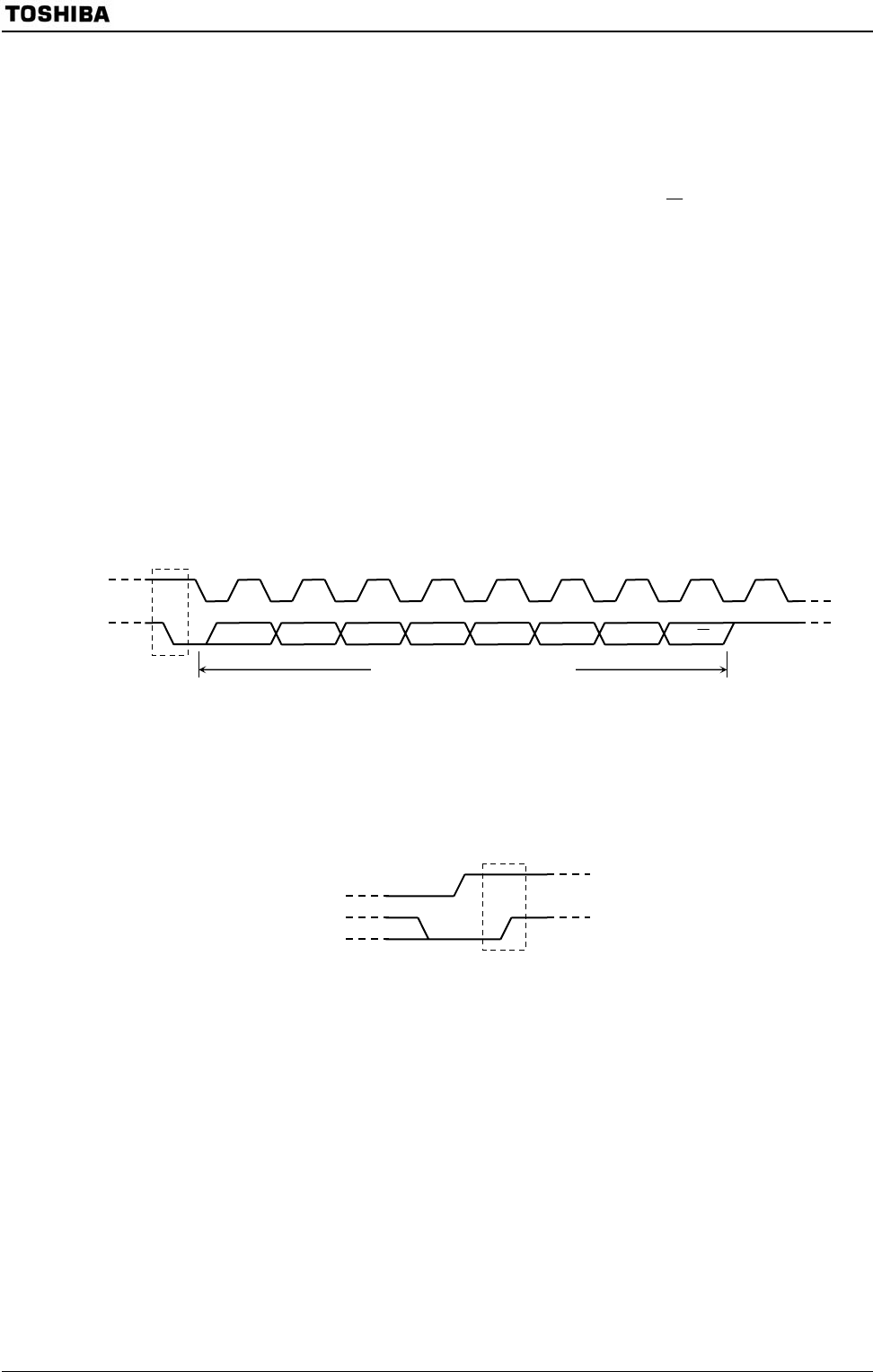

Figure 3.10.9 Generation of Start Condition and Slave Address

When programmed “0” to SBI0CR2<BB> and “111” to <MST, TRX, PIN> in during

SBI0SR<BB> is “1”, start a sequence of stop condition output. Do not modify the

contents of <MST, TRX, BB, and PIN> until a stop condition is generated on a bus.

Figure 3.10.10 Generation of Stop Condition

The state of the bus can be ascertained by reading the contents of SBI0SR<BB>.

SBI0SR<BB> will be set to 1 (Bus busy status) if a start condition has been detected on the

bus, and will be cleared to 0 if a stop condition has been detected (Bus free status).

1 2 345678 9

A6 A5 A4 A3 A2 A1 A0 R/

W

Slave address and direction bit

A

cknowledge

signal

Start condition

SCL line

SDA line

SCL line

SDA line

Stop condition