II CORE BLOCK: BCU (Bus Control Unit)

B-II-4-24 EPSON S1C33210 FUNCTION PART

DRAM Setting Conditions

The DRAM interface allows the following conditions to be selected. Although DRAM can be used in areas 8 and 7 or

areas 14 and 13, these condition are applied to all four areas and cannot be set individually for each area.

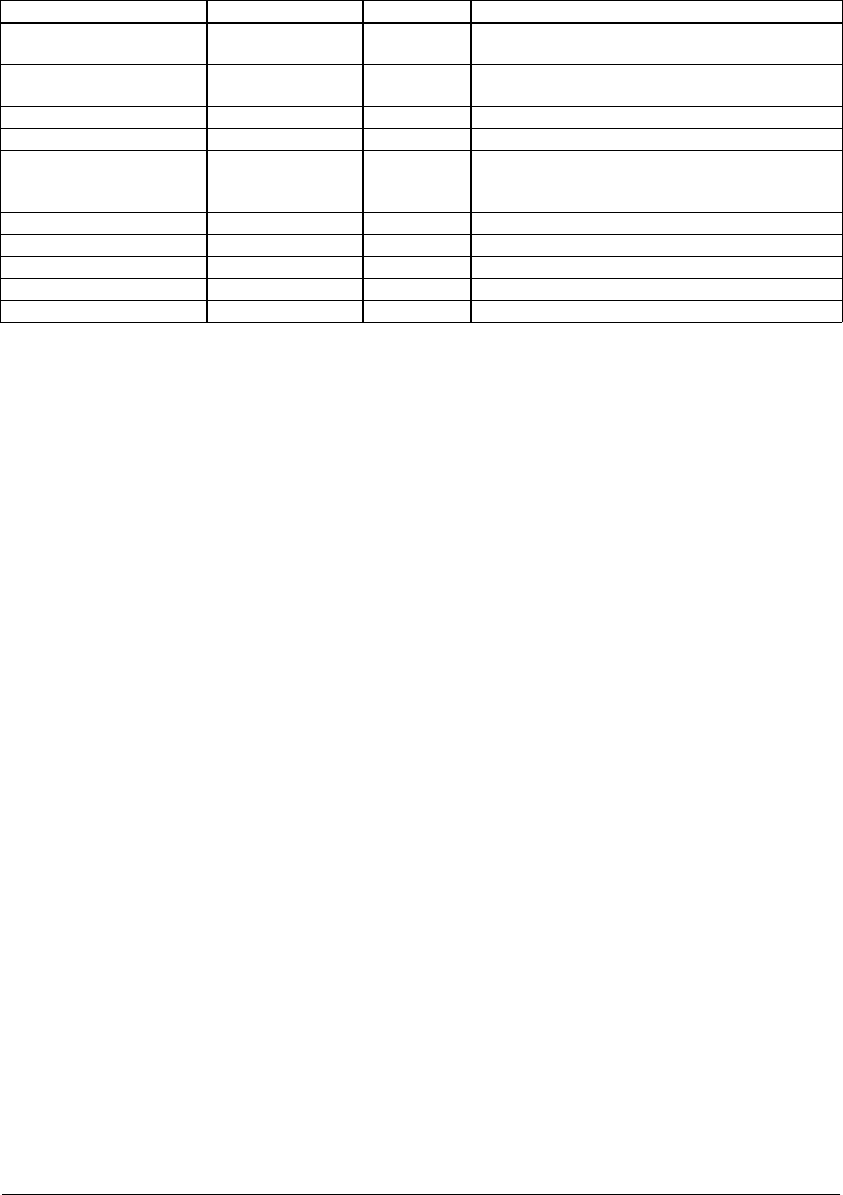

Table 4.15 DRAM Interface Parameters

Parameter Selectable condition Initial setting Control bits

Page mode EDO page mode

or Fast page mode

Fast page mode REDO(DC)/Bus control register(0x4812E)

RAS mode Successive RAS mode

or Normal mode

Normal mode CRAS(D8)/DRAM timing set-up register(0x48130)

Column address size 8, 9, 10 or 11 bits 8 bits RCA[1:0](D[B:A])/Bus control register(0x4812E)

Refresh enable Enabled or Disabled Disabled RPC2(D9)/Bus control register(0x4812E)

Refresh method Self-refresh

or CAS-before-RAS

refresh

CBR refresh RPC1(D8)/Bus control register(0x4812E)

Refresh RPC delay 2.0 or 1.0 1.0 RPC0(D7)/Bus control register(0x4812E)

Refresh RAS pulse width 2, 3, 4 or 5 cycles 2 cycles RRA[1:0](D[6:5])/Bus control register(0x4812E)

Number of RAS precharge cycles1, 2, 3 or 4 cycles 1 cycle RPRC[1:0](D[7:6])/DRAM timing set-up register(0x48130)

CAS cycle control 1, 2, 3 or 4 cycles 1 cycle CASC[1:0](D[4:3])/DRAM timing set-up register(0x48130)

RAS cycle control 1, 2, 3 or 4 cycles 1 cycle RASC[1:0](D[1:0])/DRAM timing set-up register(0x48130)

Page mode

The DRAM interface allows EDO DRAM to be connected directly. Therefore, the EDO-page mode is

supported along with the fast-page mode.

Use REDO to choose the desired page mode that suits the DRAM to be used.

REDO = "1": EDO page mode

REDO = "0": Fast page mode (default)

Successive RAS mode

For applications that require high-speed DRAM access, the DRAM interface supports a successive RAS mode.

In this mode, even when successive accesses to the DRAM are not requested by the CPU or DMA, the #RAS

signal is kept low and operation is continued without inserting any precharge cycle. Therefore, when accessing

the same page (row address) of the DRAM that has been accessed previously, the page mode remains active,

allowing read/write to be performed at high speeds.

However, to maintain the rated AC characteristics, one idle cycle is inserted when access in the page mode is

begun and when finished.

CRAS is used to set the successive RAS mode.

CRAS = "1": Successive RAS mode

CRAS = "0": Normal mode (default)

The successive RAS mode is suspended by one of the following causes:

• a refresh cycle has occurred;

• bus control is requested by an external bus master;

• the requested device and page are not compatible with DRAM memory; and

• the slp or halt instruction is executed.

If the successive RAS mode is suspended, a precharge cycle is inserted before the next bus cycle begins.

Note: When using the successive RAS mode, always be sure to use #DRD for the read signal and #DWE

for the low-byte write signal.