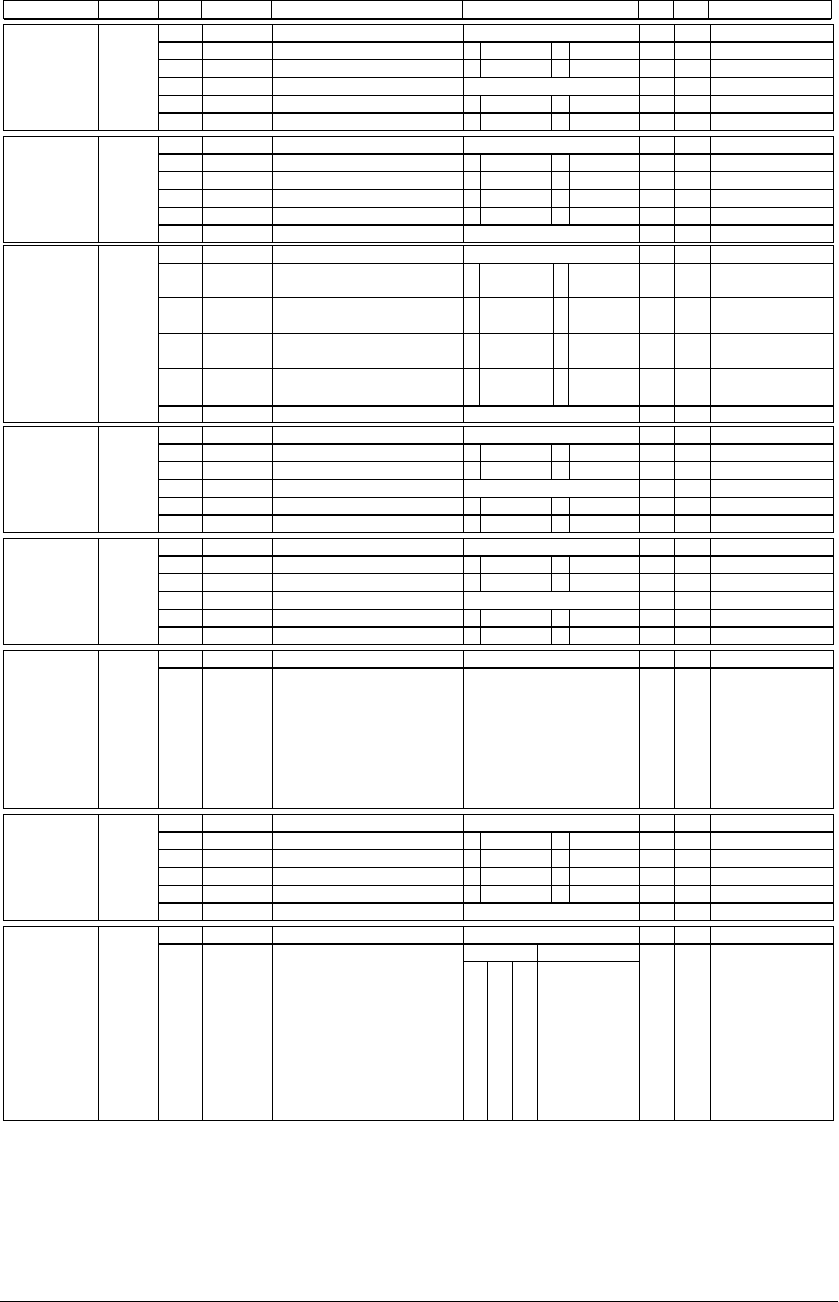

4 PERIPHERAL CIRCUITS

S1C33210 PRODUCT PART EPSON A-59

NameAddressRegister name Bit Function Setting Init. R/W Remarks

–

ERES

RESINT

–

RRXINT

RTXINT

D15–8

D7

D6

D5–2

D1

D0

–

HDLC error reset

HDLC E/S interrupt reset

–

HDLC receive interrupt reset

HDLC transmit interrupt reset

–

–

–

0

0

–

0

0

–

W

W

–

W

W

0 when being read.

0 when being read.

0200302

(HW)

1 Reset 0 Ignored

1 Reset 0 Ignored

1 Reset 0 Ignored

1 Reset 0 Ignored

HDLC interrupt

control register

–

ABRTIES

TXUEIES

HUNTIES

IDLDIES

–

D15–8

D7

D6

D5

D4

D3–0

–

Enable Abort interrupt setting

Enable TXUDR interrupt setting

Enable Hunt interrupt setting

Enable idle detection interrupt setting

–

–

–

–

0

0

0

0

–

–

R/W

R/W

R/W

R/W

–

0 when being read.

Writes of "0" are ignored

Writes of "0" are ignored

Writes of "0" are ignored

Writes of "0" are ignored

0 when being read.

0200304

(HW)

1

Enable

0

Disabled

1

Enable

0

Disabled

1

Enable

0

Disabled

1

Enable

0

Disabled

HDLC interrupt

enable settings

register

–

ABRTIEC

TXUEIEC

HUNTIEC

IDLDIEC

–

D15–8

D7

D6

D5

D4

D3–0

–

Clear Abort interrupt enable

Clear TXUDR interrupt enable

Clear Hunt interrupt enable

Clear idle detection interrupt

enable

–

–

–

–

0

0

0

0

–

1

1

1

1

0

0

0

0

–

R/W

R/W

R/W

R/W

–

0 when being read.

0 when being read.

0200306

(HW)

Clear interrupt

enable

Clear interrupt

enable

Clear interrupt

enable

Clear interrupt

enable

Ignored

Ignored

Ignored

Ignored

HDLC clear

interrupt

enable register

–

RXENS

TXENS

–

RXIES

TXIES

D15–8

D7

D6

D5–2

D1

D0

–

HDLC enable receive setting

HDLC enable transmit setting

–

HDLC enable receive interrupt setting

HDLC enable transmit interrupt setting

–

–

–

0

0

–

0

0

–

R/W

R/W

–

R/W

R/W

0 when being read.

Writes of "0" are ignored

Writes of "0" are ignored

0 when being read.

Writes of "0" are ignored

Writes of "0" are ignored

0200308

(HW)

1 Enable 0 Disable

1 Enable 0 Disable

1

Enable

0

Disabled

1

Enable

0

Disabled

HDLC transfer

settings

register

–

RXENC

TXENC

–

RXIEC

TXIEC

D15–8

D7

D6

D5–2

D1

D0

–

HDLC clear receive enable

HDLC clear transmit enable

–

HDLC clear receive interrupt enable

HDLC clear transmit interrupt enable

–

–

–

0

0

–

0

0

–

R/W

R/W

–

R/W

R/W

0 when being read.

0 when being read.

020030A

(HW)

1

Clear enable

0 Ignored

1

Clear enable

0 Ignored

1

Clear enable

0 Ignored

1

Clear enable

0 Ignored

HDLC cancel

transfer

register

–

RXADD7

RXADD6

RXADD5

RXADD4

RXADD3

RXADD2

RXADD1

RXADD0

D15–8

D7

D6

D5

D4

D3

D2

D1

D0

–

HDLC receive address

RXADD7 = MSB

RXADD0 = LSB

–

0

0

0

0

0

0

0

0

–

R/W

0 when being read.020030C

(HW)

–

0x00 to 0xFF

HDLC receive

address

register

–

ADDCE

ADDCM

IDLDE

SHFDE

–

D15–8

D7

D6

D5

D4

D3–0

–

HDLC enable address compare

HDLC address compare mode

HDLC enable idle detection

HDLC enable short frame detection

–

–

–

–

0

0

0

0

–

–

R/W

R/W

R/W

R/W

–

0 when being read.

0 when being read.

020030E

(HW)

1 Enable 0 Disable

1 Half 0 Full

1 Enable 0 Disable

1 Enable 0 Disable

HDLC receive

operation

settings

registe

r

–

RXFTH2

RXFTH1

RXFTH0

D15–3

D2

D1

D0

–

Receive queue interrupt level

–

0

0

0

–

R/W

R/W

R/W

0 when being read.0200310

(HW)

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

RXFTH[2:0] Level

8 (Full)

7

6

5

4 (Half)

3

2

1

(receive

character available)

HDLC receive

queue interrupt

threshold

register

–