III PERIPHERAL BLOCK: 16-BIT PROGRAMMABLE TIMERS

B-III-4-12 EPSON S1C33210 FUNCTION PART

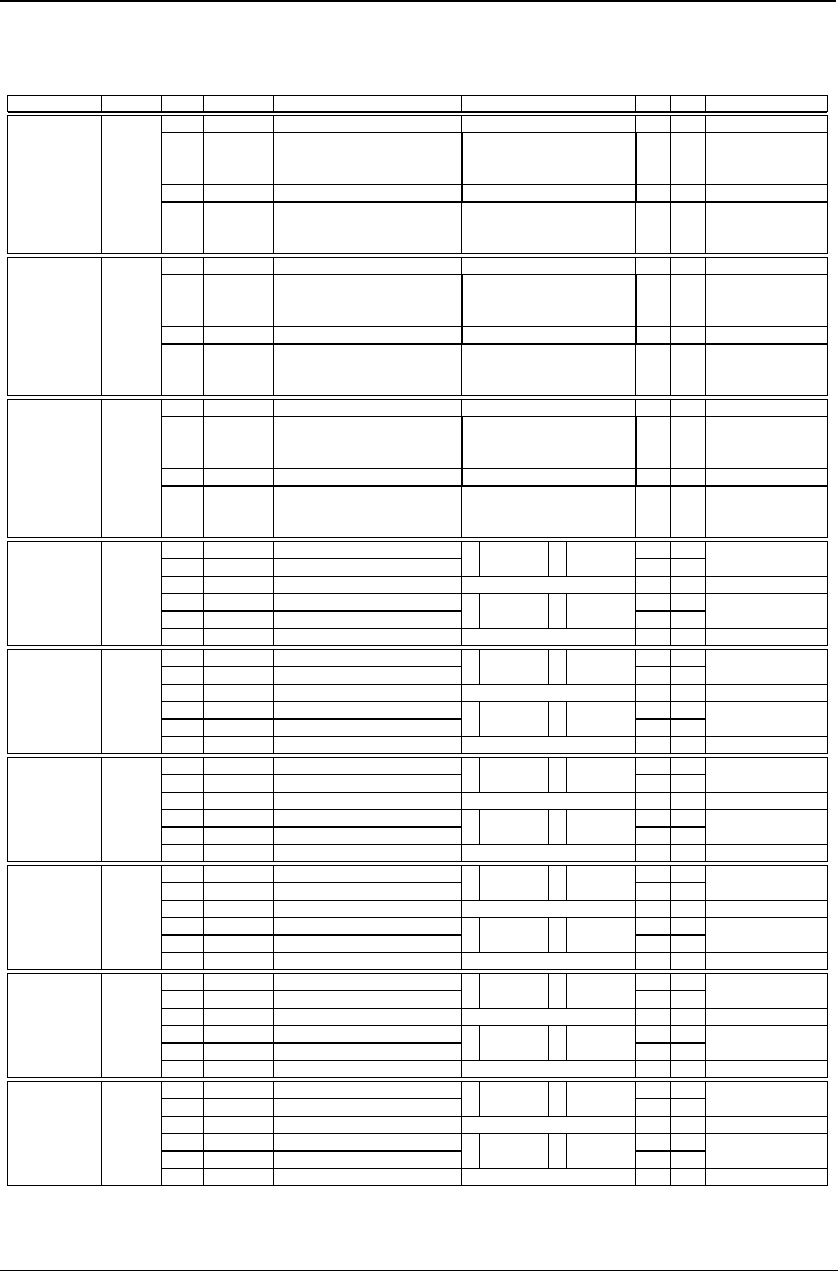

I/O Memory of 16-Bit Programmable Timers

Table 4.7 shows the control bits of the 16-bit programmable timers.

For details on the I/O memory of the prescaler used to set a clock, refer to "Prescaler".

Table 4.7 Control Bits of 16-Bit Programmable Timer

NameAddressRegister name Bit Function Setting Init. R/W Remarks

–

0 to 7

0 to 7

–

–

P16T12

P16T11

P16T10

–

P16T02

P16T01

P16T00

D7

D6

D5

D4

D3

D2

D1

D0

reserved

16-bit timer 1 interrupt level

reserved

16-bit timer 0 interrupt level

–

X

X

X

–

X

X

X

–

R/W

–

R/W

0 when being read.

0 when being read.

0040266

(B)

16-bit timer 0/1

interrupt

priority register

–

0 to 7

0 to 7

–

–

P16T32

P16T31

P16T30

–

P16T22

P16T21

P16T20

D7

D6

D5

D4

D3

D2

D1

D0

reserved

16-bit timer 3 interrupt level

reserved

16-bit timer 2 interrupt level

–

X

X

X

–

X

X

X

–

R/W

–

R/W

0 when being read.

0 when being read.

0040267

(B)

16-bit timer 2/3

interrupt

priority register

–

0 to 7

0 to 7

–

–

P16T52

P16T51

P16T50

–

P16T42

P16T41

P16T40

D7

D6

D5

D4

D3

D2

D1

D0

reserved

16-bit timer 5 interrupt level

reserved

16-bit timer 4 interrupt level

–

X

X

X

–

X

X

X

–

R/W

–

R/W

0 when being read.

0 when being read.

0040268

(B)

16-bit timer 4/5

interrupt

priority register

E16TC1

E16TU1

–

E16TC0

E16TU0

–

D7

D6

D5–4

D3

D2

D1–0

16-bit timer 1 comparison A

16-bit timer 1 comparison B

reserved

16-bit timer 0 comparison A

16-bit timer 0 comparison B

reserved

0

0

–

0

0

–

R/W

R/W

–

R/W

R/W

–

0 when being read.

0 when being read.

0040272

(B)

1 Enabled 0 Disabled

16-bit timer 0/1

interrupt

enable register

–

1 Enabled 0 Disabled

–

E16TC3

E16TU3

–

E16TC2

E16TU2

–

D7

D6

D5–4

D3

D2

D1–0

16-bit timer 3 comparison A

16-bit timer 3 comparison B

reserved

16-bit timer 2 comparison A

16-bit timer 2 comparison B

reserved

0

0

–

0

0

–

R/W

R/W

–

R/W

R/W

–

0 when being read.

0 when being read.

0040273

(B)

1 Enabled 0 Disabled

16-bit timer 2/3

interrupt

enable register

–

1 Enabled 0 Disabled

–

E16TC5

E16TU5

–

E16TC4

E16TU4

–

D7

D6

D5–4

D3

D2

D1–0

16-bit timer 5 comparison A

16-bit timer 5 comparison B

reserved

16-bit timer 4 comparison A

16-bit timer 4 comparison B

reserved

0

0

–

0

0

–

R/W

R/W

–

R/W

R/W

–

0 when being read.

0 when being read.

0040274

(B)

1 Enabled 0 Disabled

16-bit timer 4/5

interrupt

enable register

–

1 Enabled 0 Disabled

–

F16TC1

F16TU1

–

F16TC0

F16TU0

–

D7

D6

D5–4

D3

D2

D1–0

16-bit timer 1 comparison A

16-bit timer 1 comparison B

reserved

16-bit timer 0 comparison A

16-bit timer 0 comparison B

reserved

X

X

–

X

X

–

R/W

R/W

–

R/W

R/W

–

0 when being read.

0 when being read.

0040282

(B)

1 Factor is

generated

0 No factor is

generated

16-bit timer 0/1

interrupt factor

flag register

–

1 Factor is

generated

0 No factor is

generated

–

F16TC3

F16TU3

–

F16TC2

F16TU2

–

D7

D6

D5–4

D3

D2

D1–0

16-bit timer 3 comparison A

16-bit timer 3 comparison B

reserved

16-bit timer 2 comparison A

16-bit timer 2 comparison B

reserved

X

X

–

X

X

–

R/W

R/W

–

R/W

R/W

–

0 when being read.

0 when being read.

0040283

(B)

1 Factor is

generated

0 No factor is

generated

16-bit timer 2/3

interrupt factor

flag register

–

1 Factor is

generated

0 No factor is

generated

–

F16TC5

F16TU5

–

F16TC4

F16TU4

–

D7

D6

D5–4

D3

D2

D1–0

16-bit timer 5 comparison A

16-bit timer 5 comparison B

reserved

16-bit timer 4 comparison A

16-bit timer 4 comparison B

reserved

X

X

–

X

X

–

R/W

R/W

–

R/W

R/W

–

0 when being read.

0 when being read.

0040284

(B)

1 Factor is

generated

0 No factor is

generated

16-bit timer 4/5

interrupt factor

flag register

–

1 Factor is

generated

0 No factor is

generated

–