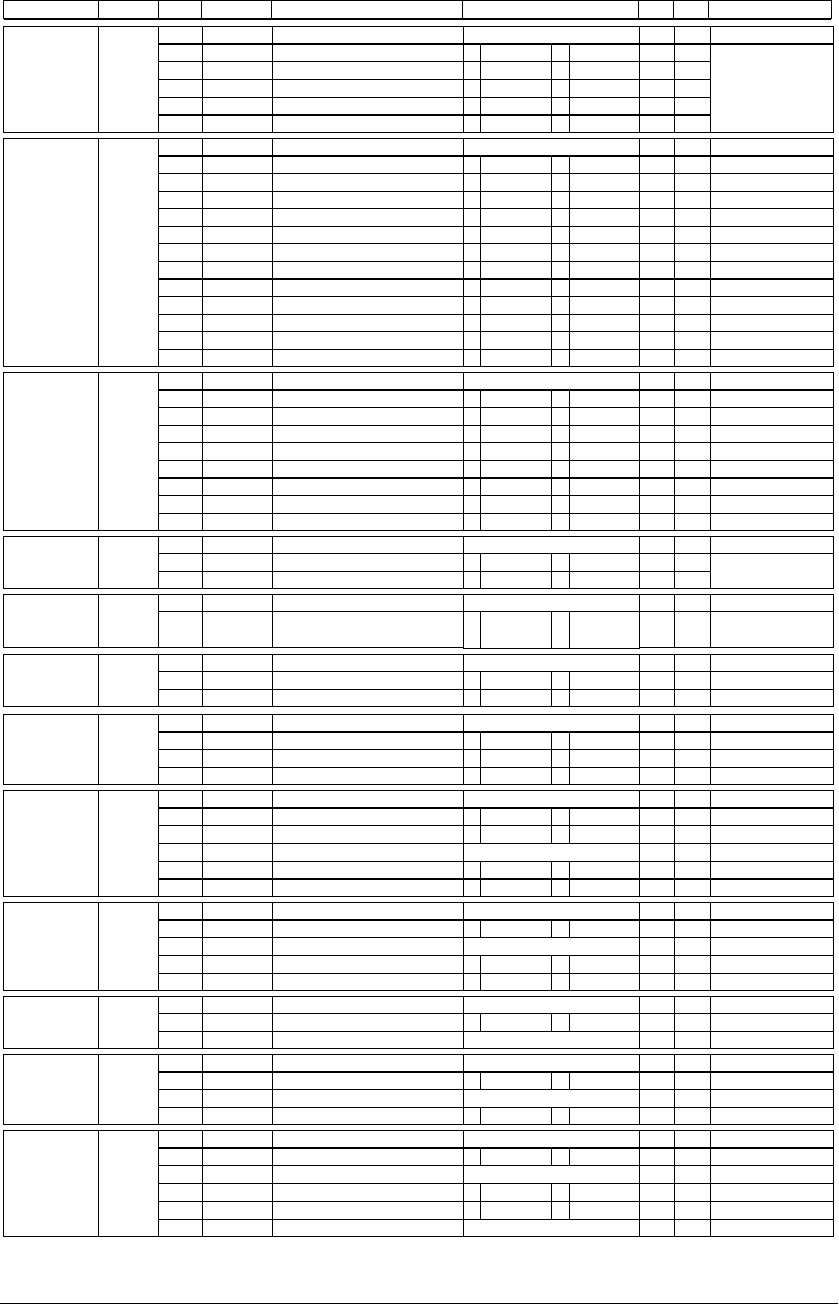

APPENDIX: I/O MAP

B-APPENDIX-44 EPSON S1C33210 FUNCTION PART

NameAddressRegister name Bit Function Setting Init. R/W Remarks

–

CP4EN4

CP4EN3

CP4EN2

CP4EN1

CP4EN0

D15–5

D4

D3

D2

D1

D0

–

Map UINT4 interrupt requests to CP4

Map UINT3 interrupt requests to CP4

Map UINT2 interrupt requests to CP4

Map UINT1 interrupt requests to CP4

Map UINT0 interrupt requests to CP4

– –

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

0 when being read.

CP4= CP

4EN4*UINT4

+CP4EN3*UINT3

+CP4EN2*UINT2

+CP4EN1*UINT1

+CP4EN0*U

INT0

0200028

(HW)

1 Enable 0 Disable

1 Enable 0 Disable

1 Enable 0 Disable

1 Enable 0 Disable

1 Enable 0 Disable

Communications

block CP4

interrupt select

register

–

RI

CTS

DCD

DSR

SDRI

SURI

SDCTS

SUCTS

SDDCD

SUDCD

SDDSR

SUDSR

D15–12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

–

RI input status

CTS input status

DCD input status

DSR input status

RI input status 1 → 0

RI input status 0 → 1

CTS input status 1 → 0

CTS input status 0 → 1

DCD input status 1 → 0

DCD input status 0 → 1

DSR input status 1 → 0

DSR input status 0 → 1

–

X

X

X

X

0

0

0

0

0

0

0

0

–

R

R

R

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.

Write "1" to clear.

Write "1" to clear.

Write "1" to clear.

Write "1" to clear.

Write "1" to clear.

Write "1" to clear.

Write "1" to clear.

Write "1" to clear.

020002A

(HW)

1 RI="L" 0 RI="H"

1 CTS="L" 0 CTS="H

1 DCD="L" 0 DCD="H"

1 DSR="L" 0 DSR="H"

1 Changed 0 No change

1 Changed 0 No change

1 Changed 0 No change

1 Changed 0 No change

1 Changed 0 No change

1 Changed 0 No change

1 Changed 0 No change

1 Changed 0 No change

Communications

block modem

status register

–

–

EDRI

EURI

EDCTS

EUCTS

EDDCD

EUDCD

EDDSR

EUDSR

D15–8

D7

D6

D5

D4

D3

D2

D1

D0

–

Enable SDRI interrupts

Enable SURI interrupts

Enable SDCTS interrupts

Enable SUCTS interrupts

Enable SDDCD interrupts

Enable SUDCD interrupts

Enable SDDSR interrupts

Enable SUDSR interrupts

–

0

0

0

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.020002C

(HW)

1 Enable 0 Disable

1 Enable 0 Disable

1 Enable 0 Disable

1 Enable 0 Disable

1 Enable 0 Disable

1 Enable 0 Disable

1 Enable 0 Disable

1 Enable 0 Disable

Communications

block modem

status interrupt

enable register

–

–

DTR

RTS

D15–2

D1

D0

–

DTR output level

RTS output level

–

0

0

–

R/W

R/W

0 when being read.

Only valid for UART

operation

020002E

(HW)

1 RTS="H" 0 RTS="L"

1 DTR="H" 0 DTR="L"

–

Communications

block modem

control register

–

STOP

D15–1

D0

–

Debugging HOLD input control

– –

0

–

R/W

0 when being read.0200032

(HW)

1

HOLD input

0

No input

Communications

block debugging

@

mode register

–

INTE

PDCINT

D15–2

D1

D0

–

Enable PDC interrupts

PDC interrupt flag

–

0

X

–

R/W

R/W

0 when being read.

Write "1" to clear

0200100

(HW)

1 Enable 0 Disable

1

Request pending

0

No interrupts

–PDC interrupt

register

–

TXBS

TXEN

RXEN

D15–3

D2

D1

D0

–

PDC transmit buffer select

Enable PDC transmit

Enable PDC receive

–

0

0

0

–

R/W

R/W

R/W

0 when being read.0200102

(HW)

PDC command

register

–

1 Buffer B 0 Buffer A

1 Enable 0 Disable

1 Enable 0 Disable

–

CRCER1

CRCER2

–

RXBB

RXBA

D15–8

D7

D6

D5–2

D1

D0

–

PDC receive CRC-16 error

PDC receive CRC-CCITT error

–

Receive buffer B status

Receive buffer A status

–

–

–

X

X

–

X

X

–

R

R

–

R

R

0 when being read.

0 when being read.

0200104

(HW)

1

CRC error

0 No error

1

CRC error

0 No error

1

Input available

0 No input

1

Input available

0 No input

PDC status

register

–

TXINTE

–

TXBS

TXEN

D15–8

D7

D6–2

D1

D0

–

Enable PHS transmit interrupt

–

PHS transmit buffer select Enable

PHS transmit

–

–

–

0

–

0

0

–

R/W

–

R/W

R/W

0 when being read.

0 when being read.

0200200

(HW)

PHS transmit

control register

1 Enable 0 Disable

1 Buffer B 0 Buffer A

1 Enable 0 Disable

–

TXINT

–

D15–8

D7

D6–0

–

PHS transmit interrupt flag

–

–

0

–

–

R/W

–

0 when being read.

Write "1" to clear

0 when being read.

0200202

(HW)

1

Request pending

0

No interrupts

–

–

PHS transmit

status register

–

RXINTE

–

RXEN

D15–8

D7

D6–1

D0

–

Enable PHS receive interrupt

–

Enable PHS receive

–

0

–

0

–

R/W

–

R/W

0 when being read.

0 when being read.

0200204

(HW)

PHS receive

control register

–

–

1 Enable 0 Disable

1 Enable 0 Disable

–

RXINT

–

CRCER

RXBS

–

D15–8

D7

D6–3

D2

D1

D0

–

PHS receive interrupt flag

–

PHS receive CRC error flag

PHS receive buffer

–

–

–

–

–

0

–

X

X

–

–

R/W

–

R

R

–

0 when being read.

Write "1" to clear

0 when being read.

0 when being read.

0200206

(HW)

PHS receive

status register

1

Request pending

0

No interrupts

1

CRC error

0 No error

1 Buffer B 0 Buffer A