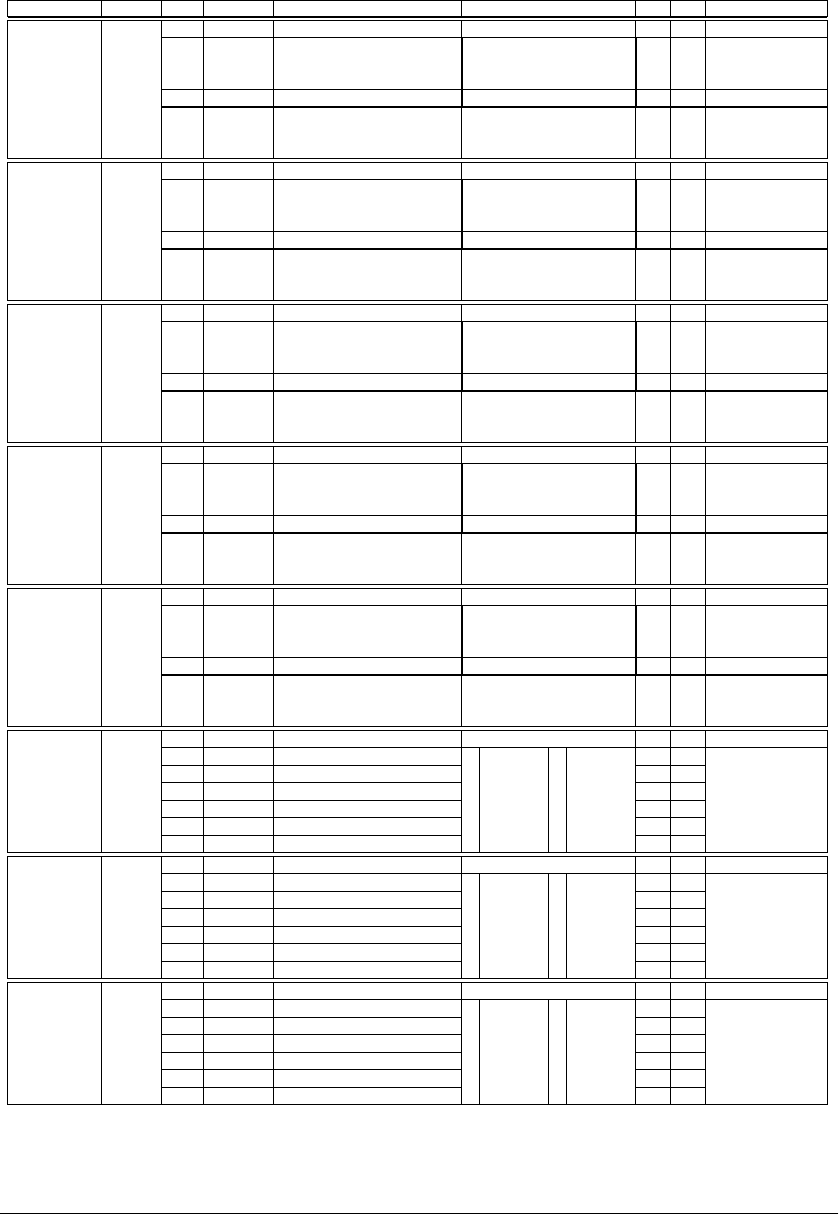

III PERIPHERAL BLOCK: INPUT/OUTPUT PORTS

S1C33210 FUNCTION PART EPSON B-III-9-17

I/O Memory for Input Interrupts

Table 9.10 shows the control bits for the port input and key input interrupts.

Table 9.10 Control Bits for Input Interrupts

NameAddressRegister name Bit Function Setting Init. R/W Remarks

–

0 to 7

0 to 7

–

–

PP1L2

PP1L1

PP1L0

–

PP0L2

PP0L1

PP0L0

D7

D6

D5

D4

D3

D2

D1

D0

reserved

Port input 1 interrupt level

reserved

Port input 0 interrupt level

–

X

X

X

–

X

X

X

–

R/W

–

R/W

0 when being read.

0 when being read.

0040260

(B)

Port input 0/1

interrupt

priority register

–

0 to 7

0 to 7

–

–

PP3L2

PP3L1

PP3L0

–

PP2L2

PP2L1

PP2L0

D7

D6

D5

D4

D3

D2

D1

D0

reserved

Port input 3 interrupt level

reserved

Port input 2 interrupt level

–

X

X

X

–

X

X

X

–

R/W

–

R/W

0 when being read.

0 when being read.

0040261

(B)

Port input 2/3

interrupt

priority register

–

0 to 7

0 to 7

–

–

PK1L2

PK1L1

PK1L0

–

PK0L2

PK0L1

PK0L0

D7

D6

D5

D4

D3

D2

D1

D0

reserved

Key input 1 interrupt level

reserved

Key input 0 interrupt level

–

X

X

X

–

X

X

X

–

R/W

–

R/W

0 when being read.

0 when being read.

0040262

(B)

Key input

interrupt

priority register

–

0 to 7

0 to 7

–

–

PP5L2

PP5L1

PP5L0

–

PP4L2

PP4L1

PP4L0

D7

D6

D5

D4

D3

D2

D1

D0

reserved

Port input 5 interrupt level

reserved

Port input 4 interrupt level

–

X

X

X

–

X

X

X

–

R/W

–

R/W

0 when being read.

0 when being read.

004026C

(B)

Port input 4/5

interrupt

priority register

–

0 to 7

0 to 7

–

–

PP7L2

PP7L1

PP7L0

–

PP6L2

PP6L1

PP6L0

D7

D6

D5

D4

D3

D2

D1

D0

reserved

Port input 7 interrupt level

reserved

Port input 6 interrupt level

–

X

X

X

–

X

X

X

–

R/W

–

R/W

0 when being read.

0 when being read.

004026D

(B)

Port input 6/7

interrupt

priority register

–

EK1

EK0

EP3

EP2

EP1

EP0

D7–6

D5

D4

D3

D2

D1

D0

reserved

Key input 1

Key input 0

Port input 3

Port input 2

Port input 1

Port input 0

– –

0

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.0040270

(B)

1 Enabled 0 Disabled

Key input,

port input 0–3

interrupt

enable register

–

EP7

EP6

EP5

EP4

ECTM

EADE

D7–6

D5

D4

D3

D2

D1

D0

reserved

Port input 7

Port input 6

Port input 5

Port input 4

Clock timer

A/D converter

– –

0

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.0040277

(B)

1 Enabled 0 Disabled

Port input 4–7,

clock timer,

A/D interrupt

enable register

–

FK1

FK0

FP3

FP2

FP1

FP0

D7–6

D5

D4

D3

D2

D1

D0

reserved

Key input 1

Key input 0

Port input 3

Port input 2

Port input 1

Port input 0

– –

X

X

X

X

X

X

–

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.0040280

(B)

1 Factor is

generated

0 No factor is

generated

Key input,

port input 0–3

interrupt factor

flag register