V DMA BLOCK: HSDMA (High-Speed DMA)

B-V-2-32 EPSON S1C33210 FUNCTION PART

D0IN1–D0IN0: Ch. 0 destination address control (D[D:C]) / Ch. 0 high-order destination address set-up register (0x4822A)

D1IN1–D1IN0: Ch. 1 destination address control (D[D:C]) / Ch. 1 high-order destination address set-up register (0x4823A)

D2IN1–D2IN0: Ch. 2 destination address control (D[D:C]) / Ch. 2 high-order destination address set-up register (0x4824A)

D3IN1–D3IN0: Ch. 3 destination address control (D[D:C]) / Ch. 3 high-order destination address set-up register (0x4825A)

Control the incrementing or decrementing of the memory address.

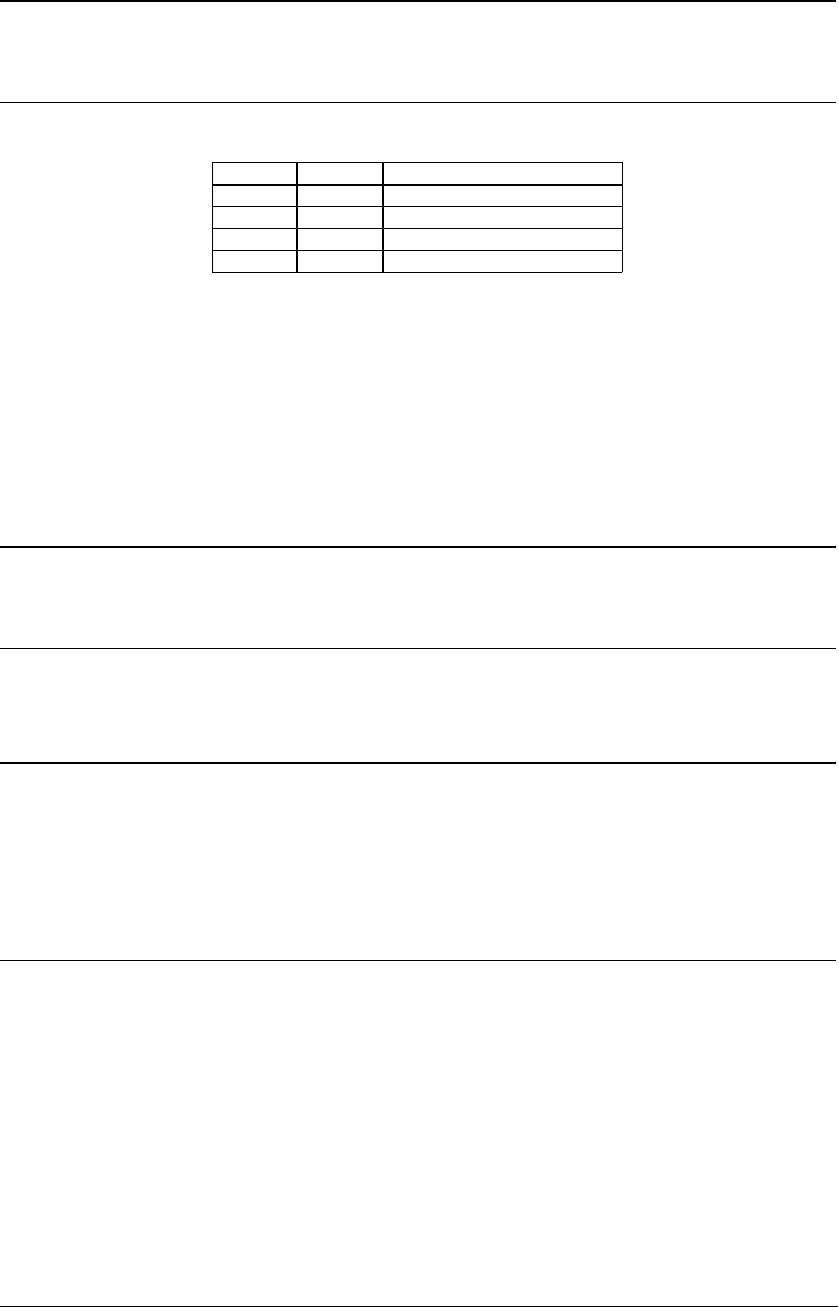

Table 2.9 Address Control

DxIN1 DxIN0 Address control

1 1 Increment without initialization

1 0 Increment with initialization

0 1 Decrement without initialization

0 0 Fixed

In dual-address mode, this setting applies to the destination address. In single-address mode, these bits are not used.

When "address fixed" (00) is selected, the destination address is not changed by a data transfer performed. Even

when transferring multiple data, the transfer data is always written to the same address.

When "address increment" (11 or 10) is selected in single and successive transfer modes, the destination address is

incremented by an amount equal to the data size set by DATSIZEx when one data transfer is completed.

When "address decrement" (01) is selected, the destination address is decremented in the same way.

In block transfer mode too, the destination address is incremented or decremented when one data unit is transferred.

However, if DxIN is set to "10", the destination address that has been incremented during a block transfer recycles

back to the initial value when the block transfer is completed.

At initial reset, DxIN is set to "00" (Fixed).

BLKLEN07–BLKLEN00:

Ch. 0 block length/transfer counter[7:0] (D[7:0]) / Ch. 0 transfer counter register (0x48220)

BLKLEN17–BLKLEN10: Ch. 1 block length/transfer counter[7:0] (D[7:0]) / Ch. 1 transfer counter register (0x48230)

BLKLEN27–BLKLEN20: Ch. 2 block length/transfer counter[7:0] (D[7:0]) / Ch. 2 transfer counter register (0x48240)

BLKLEN37–BLKLEN30: Ch. 3 block length/transfer counter[7:0] (D[7:0]) / Ch. 3 transfer counter register (0x48250)

In block transfer mode, these bits are used to specify a transfer block size. A transfer operation invoked by one

trigger is completed after transferring one block of data of the size set by BLKLENx.

In single or successive transfer mode, these bits are used to specifythe 8 low-order bits of the transfer counter.

At initial reset, these bits are not initialized.

TC0_L7–TC0_L0: Ch. 0 transfer counter[7:0]/[15:8] (D[F:8]) / Ch. 0 transfer counter register (0x48220)

TC0_H7–TC0_H0: Ch. 0 transfer counter[15:8]/[23:16] (D[F:8]) / Ch. 0 control register (0x48222)

TC1_L7–TC1_L0: Ch. 1 transfer counter[7:0]/[15:8] (D[F:8]) / Ch. 1 transfer counter register (0x48230)

TC1_H7–TC1_H0: Ch. 1 transfer counter[15:8]/[23:16] (D[F:8]) / Ch. 1 control register (0x48232)

TC2_L7–TC2_L0: Ch. 2 transfer counter[7:0]/[15:8] (D[F:8]) / Ch. 2 transfer counter register (0x48240)

TC2_H7–TC2_H0: Ch. 2 transfer counter[15:8]/[23:16] (D[F:8]) / Ch. 2 control register (0x48242)

TC3_L7–TC3_L0: Ch. 3 transfer counter[7:0]/[15:8] (D[F:8]) / Ch. 3 transfer counter register (0x48250)

TC3_H7–TC3_H0: Ch. 3 transfer counter[15:8]/[23:16] (D[F:8]) / Ch. 3 control register (0x48252)

Set the data transfer count.

In block transfer mode, TCx_L[7:0] is bits[7:0] of the transfer counter, and TCx_H[7:0] is bits[15:8] of the transfer

counter.

In single or successive transfer mode, TCx_L[7:0] is bits[15:8] of the transfer counter, and TCx_H[7:0] is bits[23:16]

of the transfer counter. The 8 low-order bits are specified by BLKLENx[7:0].

This counter is decremented each time a DMA transfer in the corresponding channel is performed. When the

counter reaches 0, an interrupt factor is generated. In single-address mode, the end-of-transfer signal is output from

the #DMAENDx pin at the same time.

Even when the counter is 0, a DMA request is accepted and the counter is decremented to "0xFFFF" (or

"0xFFFFFF").

Be sure to disable DMA transfers (HSx_EN = "0") before writing and reading to and from the counter.

At initial reset, these bits are not initialized.